# F&eIT Series

# Isolated Analog Output Module **DAI12-4(FIT)GY**User's Manual

CONTEC CO.,LTD.

# **Check Your Package**

Thank you for purchasing the CONTEC product.

The product consists of the items listed below.

Check, with the following list, that your package is complete. If you discover damaged or missing items, contact your retailer.

Product Configuration List

- Module ...1

- First Step Guide ...1

- CD-ROM [F&eIT Series Setup Disk] \*1...1

- Interface connector plugs ...2

- The CD-ROM contains various software and User's Manual (this manual)

Interface connector plug First step guide [F&eIT Series Setup Disk]

# **Copyright**

Copyright 2001 CONTEC CO., LTD. ALL RIGHTS RESERVED

No part of this document may be copied or reproduced in any form by any means without prior written consent of CONTEC CO., LTD.

CONTEC CO., LTD. makes no commitment to update or keep current the information contained in this document.

The information in this document is subject to change without notice.

All relevant issues have been considered in the preparation of this document. Should you notice an omission or any questionable item in this document, please feel free to notify CONTEC CO., LTD.

Regardless of the foregoing statement, CONTEC assumes no responsibility for any errors that may appear in this document nor for results obtained by the user as a result of using this product.

# **Trademarks**

F&eIT is a registered trademark or trademark of CONTEC CO., LTD. Other company and product names that are referred to in this manual are generally trademarks or registered trade trademark.

# **Table of Contents**

| Copyright                                | i  |

|------------------------------------------|----|

| Trademarks                               |    |

| Product Configuration                    |    |

| Table of Contents                        |    |

| 1. Introduction                          |    |

| Features                                 | 1  |

| Functions and control method by          | 1  |

| controller connected                     | 2  |

| Limited One-Year Warranty                |    |

| How to Obtain Service                    | 4  |

| Liability                                |    |

| Handling Precautions                     | 5  |

| About the Manual                         |    |

| 2. Module Nomenclature and Settings      | 7  |

|                                          |    |

| Nomenclature of Module Components        | 7  |

| Setting a Device ID                      | 8  |

| Setup Method                             |    |

| LED Indicator                            | 8  |

| 3. Connecting to an External Device      | 9  |

| Interface Connector                      | 9  |

| How to Connect an Interface Connector    | 9  |

| Signal Layout on the Interface Connector | 10 |

| Connecting an Analog Output Signal       | 11 |

| Connecting a Voltage Output              | 11 |

| Connecting a Current Output              | 13 |

| 4. Using the I/O Address Map             | 15 |

| Starting I/O Address                     | 15 |

| List of I/O Address Maps                 | 16 |

| Specifications Common to F&eIT Products  | 18 |

| Product Information                      | 18 |

| Overview of the D/A Conversion Function  |    |

| Details on the Analog Output Status      | 28 |

| List of Commands     | 31       |

|----------------------|----------|

|                      |          |

| Software Mode        |          |

|                      | ots)     |

|                      | upts) 37 |

|                      | Map43    |

| Module Settings Area | 44       |

|                      | a47      |

|                      | 49       |

| Examples             | 51       |

| 6. System Reference  | 55       |

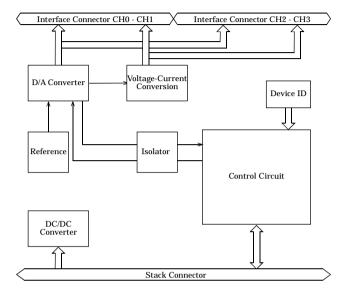

| Block Diagram        | 55       |

| Specifications       | 55<br>56 |

|                      | 58       |

# 1. Introduction

Congratulations on your recent purchase of an Insulator Digital Output Module.

The DAI12-4(FIT)GY can control external devices by converting digital data that is output from a, F&eIT-series controller module <CPU-CAxx(FIT)GY,

CPU-SBxx(FIT)GY etc> into either voltage or current-based analog signals. The insulation between external signals and the Controller Module permits the use of the Controller Module without compromising the communications features of the latter.

By reading this manual carefully, please build a system by creating applications programs, setting the switches, and connecting the module to external devices.

### **Features**

- -The output range is common to different channels, and can be selected from five output ranges: 0 10V, 0 5V, ±10V, ±5V, and 0 20mA.

- -A rotary switch that is provided allows you to set device IDs to help you keep track of device numbers.

- -The system incorporates a screwless connector plug that allows you to easily attach and detach wires without using any special tools.

- -Similar to other F&eIT series products, the system, in the module itself, incorporates a 35mm DIN rail mounting mechanism as a standard item. A connection to a controller module can be effected on a lateral, stack basis in a unique configuration, which permits a simple, smart system configuration without the need for a backplane board.

# Functions and control method by controller connected

The DAI12-4(FIT)GY can be connected to a variety of controllers.

Micro Controller Unit : CPU-SBxx(FIT)GY

I/O Controller Module : CPU-CAxx(FIT)GY

Monitoring & Control Server Unit : SVR-MMF2(FIT)

Monitoring & Control Server Unit : SVR-MMF(FIT)GY

Isolated Analog Output Module for USB : DAI12-4 (USB)GY

I/O Controller Module with USB : CPU-CA10(USB)GY

The functions and control of the DAI12-4(FIT)GY vary with the controller to which the DAI12-4(FIT)GY is connected.

### Functions available with each controller connected

|                                                          | CPU,SE | CPU.CA | SVR-MA | SVR-MAL | DAI12.40. | CPU-CAL | Y O(U/SB)CF |

|----------------------------------------------------------|--------|--------|--------|---------|-----------|---------|-------------|

| Software input range setting                             | 0      | О      |        |         | 0         | 0       |             |

| D/A conversion with software command                     | 0      | 0      |        |         | 0         | 0       |             |

| Continuous D/A conversion using the internal pacer clock | 0 *2   |        | *1     | *1      | 0 *3      |         |             |

| Multi-channel simultaneous output function               | 0      |        |        |         | 0         | 0       |             |

| Interrupt function                                       | 0      |        |        |         |           |         |             |

| Device ID setting range                                  | 0 - 7  | 0 - 7  | 0 - 7  | 0 - 7   | 1 - 3     | 0 - 7   |             |

<sup>\*1</sup> For the function available, refer to the reference manual for the SVR-MMF2(FIT), SVR-MMF(FIT)GY.

The setting range is from 1000 to 1,073,741,000 microseconds.

<sup>\*2</sup> Pacer clock setting: 10 - 1,073,741,824 microseconds

<sup>\*3</sup> Using the sampling timer built in the DAI12-4(USB)GY

#### $^{Cp_{U,C_{A}}}_{U(U,S_{B})G_{Y}}$ CPU.CARKETIJGY $S_{VR-MMF/FTD/GY}$ SVR-MMF2(FTT) $b_{^{4II24}USB|GY}$ Control using the I/O address map Control using the memory address map o FIT Protocol 0 API-CAP(W32) 0 Control via the Windows driver API-SBP(W32) o API-USBP(WDM) o o Control over the web 0

### Control method by controller connected

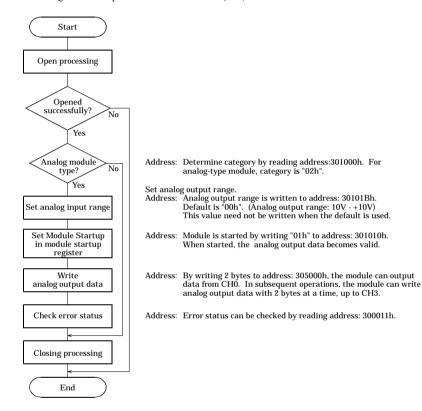

### Control using the I/O address map

When connected to the CPU-SBxx(FIT)GY, the DAI12-4(FIT)GY can receive I/O instructions directly from the controller module. For details, see Chapter 4 "Using the I/O Address Map".

### Control using the memory address map

When connected to the CPU-CAxx(FIT)GY, the DAI12-4(FIT)GY can be accessed from the host computer over the network.

The DAI12-4(FIT)GY is assigned with its device ID in the memory managed by the controller module. The application running on the host computer controls the module by reading/writing the memory managed by the controller module. For details, see Chapter 5 "Using the Memory Address Map".

### Control via the Windows driver

For the functions and settings available when using the Windows driver, refer to the reference manual and online help for each module.

#### Control over the web

You can monitor collected data and manage the log over the web. You can use your familiar browser to easily make various settings. For details, refer to the reference manual for the SVR-MMF2(FIT), SVR-MMF(FIT)GY.

The API-SBP(W32) is included in the development kit DTK-SBxx(FIT): the other drivers are bundled with each controller.

## **Limited One-Year Warranty**

CONTEC F&eIT products are warranted by CONTEC CO., LTD. to be free from defects in material and workmanship for up to one year from the date of purchase by the original purchaser.

Repair will be free of charge only when this product is returned freight prepaid with a copy of the original invoice and a Return Merchandise Authorization to the distributor or the CONTEC group office, from which it was purchased.

This warranty is not applicable for scratches or normal wear, but only for the electronic circuitry and original products.

The warranty is not applicable if the device has been tampered with or damaged through abuse, mistreatment, neglect, or unreasonable use, or if the original invoice is not included, in which case repairs will be considered beyond the warranty policy.

### **How to Obtain Service**

For replacement or repair, return the device freight prepaid, with a copy of the original invoice. Please obtain a Return Merchandise Authorization Number (RMA) from the CONTEC group office where you purchased before returning any product.

\* No product will be accepted by CONTEC group without the RMA number.

### Liability

The obligation of the warrantor is solely to repair or replace the product. In no event will the warrantor be liable for any incidental or consequential damages due to such defect or consequences that arise from inexperienced usage, misuse, or malfunction of this device.

# **Handling Precautions**

Take the following precautions when handling this module.

- Do not modify the module. CONTEC will bear no responsibility for any problems, etc., resulting from modifying this module.

- Do not use or store the equipment in a hot or cold place, or in a place that is subject to severe temperature changes (Operating temperature range: 0 50°C).

- Do not use or store the equipment in a place subject to direct sunlight or near a heating device, such as a stove.

- Do not use or store the equipment in a dusty or humid place. (Operating humidity range: 10 90%RH, No condensation)

- As this product contains precision electronic components, do not use or store in environments subject to shock or vibration.

- Do not use or store the product near equipment generating a strong magnetic field or radio waves.

- If you notice any strange odor or overheating, please unplug the power cord immediately.

- In the event of an abnormal condition or malfunction, please consult the dealer from whom the equipment was purchased.

- To avoid electric shock, please do not touch the system with a wet hand.

- Do not open the module casing. CONTEC will disclaim any responsibility for equipment whose casing has been opened.

- To prevent damage, please do not subject the module to impact or bend it.

- To prevent contact malfunction, please do not touch the metallic pins on the external module connector.

- The module contains switches that need to be properly set. Before using the module, please check its switch settings.

- To avoid malfunction, please do not change the module switch settings in an unauthorized manner.

- Do not operate the device module when the power for the Controller Module is on.

To avoid malfunction, please be sure to turn off the power for the Controller Module.

### FCC PART 15 Class A Notice

### NOTE

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in commercial environment.

This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference at his own expense.

### WARNING TO USER

Change or modifications not expressly approved the manufacturer can void the user's authority to operate this equipment.

### **About the Manual**

This manual consists of the following chapters:

Introduction Chapter 1

Chapter 2 Module Nomenclature and Settings

Explains the nomenclature of the components of the Module and their

operations.

Chapter 3 Connecting to an External Device

Explains interface connectors and provides tips on how to make a

connection to an external device.

Chapter 4 Using the I/O Address Map

Explains I/O port bit assignments and the definitions of the bits when

the Module is used as a CPU-SBxx(FIT)GY module.

Chapter 5 Using the Memory Address Map

> Explains the module setting area, the information area, and the basic input data area when the Module is used as a CPU-CAxx(FIT)GY

module.

Chapter 6 System Reference

Explains module specifications and circuit block diagrams.

# 2. Module Nomenclature and Settings

# **Nomenclature of Module Components**

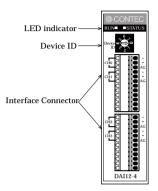

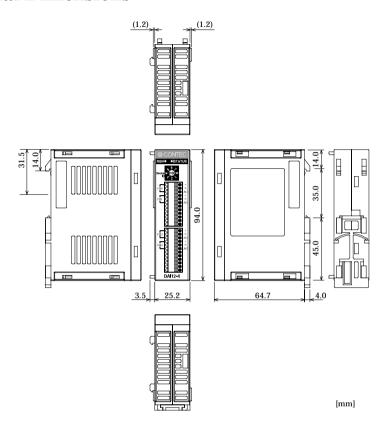

Figure 2.1 shows the names of module components. In the figure, the indicated switch settings represent factory settings.

Figure 2.1. Names of Module Components

# **Setting a Device ID**

The controller module distinguishes and keeps track of the modules that are connected to it by assigning device IDs to them. Each module, therefore, should be assigned a unique ID.

A Device ID can be assigned in a 0 - 7 range, so that a maximum of eight modules can be distinguished.

To connect the DAI12-4(FIT)GY to the DAI12-4(USB)GY, assign a device ID between 1 and 3.

The factory setting for the Device ID is [0].

### **Setup Method**

A Device ID can be set by turning the rotary switch on the device face. To set a Device ID, turn the switch knob.

Figure 2.2. Setting a Device ID

# **LED Indicator**

RUN: Indicates that the DAI12-4(FIT)GY can be controlled from the

Controller Module (green).

STATUS: This light comes on when a D/A conversion error occurs (red).

# 3. Connecting to an External Device

# **Interface Connector**

### **How to Connect an Interface Connector**

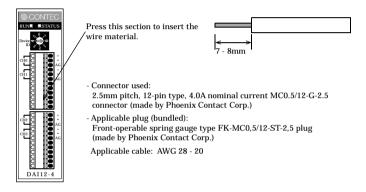

When connecting the Module to an external device, you can use the supplied connector plug. When wiring the Module, strip off approximately 7 - 8 mm of the covering for the cable, and insert the bare wire by pressing the orange button on the connector plug. Releasing the orange button after the wire is inserted to fix the cable. Compatible wires are AWG 28 - 20.

Figure 3.1. Connecting an Interface Connector and Connectors That Can Be Used

### Note!

Removing the connector plug by grasping the cable can break the wire.

# **Signal Layout on the Interface Connector**

The Module can be connected to an external device using a 12pin (1 group) connector that is provided on the Module face.

Figure 3.2. Signal Layout on the Interface Connector

# **Connecting an Analog Output Signal**

### **Connecting a Voltage Output**

### Connecting with a Flat Cable

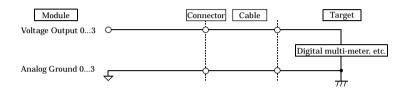

This example involves connecting the voltage output and the analog ground for each channel to the input and the ground of an external device, using a flat cable.

Figure 3.3. Connecting a Voltage Output (Flat Cable)

### Connecting with a coaxial cable

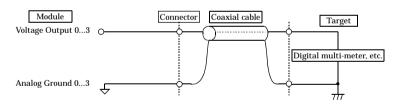

A coaxial cable can be used in situations where the module is at a relatively large distance from the external device or when the noise immunity of the module must be improved. In this case, the voltage output and the analog ground for each channel are connected to the input and the ground, respectively, of the external device by using the core wire and the shield braid of the coaxial cable.

Figure 3.4. Connecting a Voltage Output (Coaxial Cable)

### Notes!

- When the power is turned on or the module is reset, the voltage output signal will be 0V.

- To avoid any malfunction, the voltage output signal should not be connected to the analog ground.

- To avoid any malfunction, the voltage output signal should not be connected to another analog output signal or the output signal of an external device.

- To avoid any malfunction, the connector plug should not be attached or detached when the power for the module or the external device is on.

- The maximum current capacity for a voltage output signal is ±5mA. To avoid any

malfunction, do not connect an external device that generates a load exceeding this

range.

- In situations where the connecting cable is subject to the effects of noise, the

accurate voltage output can fail. The connecting cable should be installed away

from any source of noise.

- In situations where the connecting cable is excessively long, the accurate voltage output can fail. Use a cable that is as short as possible.

- Because the D/A converter in the module does not contain a built-in deglitcher, a glitch can sometimes occur.

### **Connecting a Current Output**

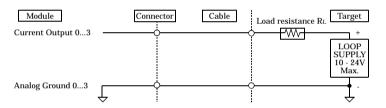

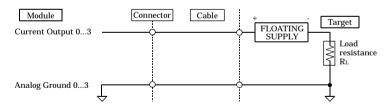

### **Example of Connecting a Negative Load Resistor**

Two types of connection methods can be employed: fixed load and floating load. If the module is used as a load resistance, multiple current loops can be implemented by using the same power supply. The use of current output requires an external power supply (10 - 24V). In such a case, a power supply with a small ripple should be used in order to avoid an adverse impact on the conversion accuracy due to a large power supply ripple.

The load resistance RL that is connected to the current output of each channel should be less than  $500\Omega$ , including the wire resistance.

### **Example of Connecting with a Flat Cable**

Use a flat cable to connect the voltage output and the analog ground of each channel to the load resistance RL.

Figure 3.5. Connecting to a Floating Load (Flat Cable)

Figure 3.6. Connecting to a Fixed Load (Flat Cable)

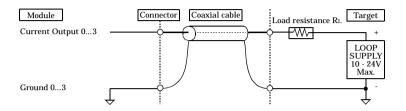

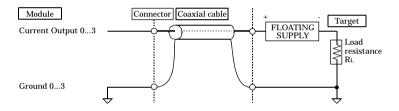

### **Example of Connecting with a Coaxial Cable**

A coaxial cable can be used in situations where the module is at a relatively large distance from the external device or when the noise immunity of the module must be improved. In this case, the current output and the analog ground for each channel are connected to the load resistance RL of the external device by using the core wire and the shield braid of the coaxial cable.

Figure 3.7. Connecting to a Floating Load (Coaxial Cable)

Figure 3.8. Connecting to a Fixed Load (Coaxial Cable)

### Notes!

- When the power is turned on or the module is reset, the current output signal will be 0 mA.

- To avoid any malfunction, the current output signal should not be connected to the analog ground.

- To avoid any malfunction, the current output signal should not be connected to another analog output signal or the output signal of an external device.

- To avoid any malfunction, the connector plug should not be attached or detached when the power for the module or the external device is on.

- In situations where the connecting cable is subject to the effects of noise, the accurate current output can fail.

- The connecting cable should be installed away from any source of noise.

# 4. Using the I/O Address Map

# **Starting I/O Address**

When connected to a CPU-SBxx(FIT)GY, the DAI12-4(FIT)GY can directly receive I/O commands from the controller module. Depending on how the Device ID is set, the occupied I/O address takes the values indicated below.

Because the address bus on which the I/O address space is specified is not fully decoded in continued 16 bits, four starting I/O addresses exist in each Device ID.

If the Device ID is set to 0, one of the four addresses (0800h, 0840h, 0880h, or 08C0h) will be used as a starting I/O address.

Table 4.1. List of Starting I/O Addresses

| ID No. | Occupied I/O address       |               |               |               |  |  |  |

|--------|----------------------------|---------------|---------------|---------------|--|--|--|

| 0      | 0800h - 081Fh(recommended) | 0840h - 085Fh | 0880h - 089Fh | 08C0h - 08DFh |  |  |  |

| 1      | 1800h - 181Fh(recommended) | 1840h - 185Fh | 1880h - 189Fh | 18C0h - 18DFh |  |  |  |

| 2      | 2800h - 281Fh(recommended) | 2840h - 285Fh | 2880h - 289Fh | 28C0h - 28DFh |  |  |  |

| 3      | 3800h - 381Fh(recommended) | 3840h - 385Fh | 3880h - 389Fh | 38C0h - 38DFh |  |  |  |

| 4      | 4800h - 481Fh(recommended) | 4840h - 485Fh | 4880h - 489Fh | 48C0h - 48DFh |  |  |  |

| 5      | 5800h - 581Fh(recommended) | 5840h - 585Fh | 5880h - 589Fh | 58C0h - 58DFh |  |  |  |

| 6      | 6800h - 681Fh(recommended) | 6840h - 685Fh | 6880h - 689Fh | 68C0h - 68DFh |  |  |  |

| 7      | 7800h - 781Fh(recommended) | 7840h - 785Fh | 7880h - 789Fh | 78C0h - 78DFh |  |  |  |

For detailed specifications on the I/O space that is managed by the controller module, see the controller module manual.

# **List of I/O Address Maps**

### **Input Port**

| Starting<br>I/O addres | s D07  | D06     | D05                  | D04                  | D03               | D02               | D01                  | D00               |

|------------------------|--------|---------|----------------------|----------------------|-------------------|-------------------|----------------------|-------------------|

| input                  | 201    | Product |                      | 201                  | 200               |                   | on Data              | 500               |

| +0<br>(+00h)           | 0      | 0       | 1                    | 0                    | Revision<br>Data3 | Revision<br>Data2 | Revision<br>Data1    | Revision<br>Data0 |

| +1                     |        |         |                      | Product II           | ) Number          |                   |                      |                   |

| +1<br>(+01h)           | 0      | 0       | 0                    | 0                    | 0                 | 0                 | 0                    | 1                 |

| +2                     |        |         |                      | Interrup             | t Status          |                   |                      |                   |

| +2<br>(+02h)           | Enable | Status  | 0                    | 0                    | 0                 | IRQ9              | IRQ7                 | IRQ5              |

| +3<br>(+03h)           |        |         |                      |                      |                   |                   |                      |                   |

| ÷                      |        |         |                      | (Not av              | ailable)          |                   |                      |                   |

| +21<br>(+15h)          |        |         |                      | A 1 . 0              |                   |                   |                      |                   |

| <b></b> +22            |        |         | D                    |                      | tput Status       |                   | F 1 6                | D . C .           |

| +22<br>(+16h)          | 0      | 0       | Pacer<br>Clock Error | Pacer<br>Clock Input | 0                 | 0                 | End of<br>Conversion | Data Set<br>Busy  |

| +23<br>(+17h)          |        |         |                      |                      |                   |                   |                      |                   |

| ÷                      |        |         |                      | (Not av              | ailable)          |                   |                      |                   |

| +31<br>(+1Fh)          |        |         |                      |                      |                   |                   |                      |                   |

Figure 4.1. Input Port

### **Output Port**

| Starting<br>I/O Addre                                                                       | SS D07                                              | D06                                             | Dor                                      | D04                                                                                                                                               | Dog                                                                                                          | Dog                                      | D01                                                 | Doo                                                        |  |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------|------------------------------------------------------------|--|

| output<br>+0                                                                                | ss D07                                              | D00                                             | D05                                      | D04                                                                                                                                               | D03                                                                                                          | D02                                      | D01                                                 | D00                                                        |  |

| (+00h)                                                                                      | (Nat - Nama A)                                      |                                                 |                                          |                                                                                                                                                   |                                                                                                              |                                          |                                                     |                                                            |  |

| +1:                                                                                         | (Not allowed)                                       |                                                 |                                          |                                                                                                                                                   |                                                                                                              |                                          |                                                     |                                                            |  |

| (+01h)<br>+2                                                                                |                                                     |                                                 |                                          | Interru                                                                                                                                           | pt Data                                                                                                      |                                          |                                                     |                                                            |  |

| (+02h)                                                                                      | Enable                                              | N/A                                             | N/A                                      | N/A                                                                                                                                               | N/A                                                                                                          | IRQ9                                     | IRQ7                                                | IRQ5                                                       |  |

| _                                                                                           | Enable                                              | IN/A                                            | IN/A                                     | IN/A                                                                                                                                              | IN/A                                                                                                         | Data                                     | Data                                                | Data                                                       |  |

| +3<br>(+03h)                                                                                |                                                     |                                                 |                                          |                                                                                                                                                   |                                                                                                              |                                          |                                                     |                                                            |  |

| +15                                                                                         |                                                     |                                                 |                                          | (Not al                                                                                                                                           | lowed)                                                                                                       |                                          |                                                     |                                                            |  |

| (+0Fh)                                                                                      |                                                     |                                                 |                                          |                                                                                                                                                   |                                                                                                              |                                          |                                                     |                                                            |  |

| +16<br>(+10h)                                                                               | c :                                                 |                                                 |                                          | 1                                                                                                                                                 | t Data (Lower                                                                                                |                                          | c :                                                 | Conversion                                                 |  |

| (+1011)                                                                                     | Conversion<br>Data 07                               | Conversion<br>Data 06                           | Conversion<br>Data 05                    | Conversion<br>Data 04                                                                                                                             | Conversion<br>Data 03                                                                                        | Conversion<br>Data 02                    | Conversion<br>Data 01                               | Data 00<br>(LSB)                                           |  |

| +17                                                                                         |                                                     | •                                               | A                                        | analog Outpu                                                                                                                                      | t Data (Upper                                                                                                | •)                                       |                                                     | 1222                                                       |  |

| (+11h)                                                                                      | N/A                                                 | N/A                                             | N/A                                      | N/A                                                                                                                                               | Conversion<br>Data 11<br>(MSB)                                                                               | Conversion<br>Data 10                    | Conversion<br>Data 09                               | Conversion<br>Data 08                                      |  |

| +18                                                                                         |                                                     |                                                 |                                          | Channa                                                                                                                                            | al Data                                                                                                      |                                          |                                                     |                                                            |  |

| (+12h)                                                                                      | All                                                 | End                                             | N/A                                      | N/A                                                                                                                                               | N/A                                                                                                          | Channel                                  | Channel                                             | Channel                                                    |  |

|                                                                                             | Channel                                             | Channel                                         | IN/A                                     | IN/A                                                                                                                                              | IN/A                                                                                                         | Data 02                                  | Data 01                                             | Data 00                                                    |  |

| +19                                                                                         |                                                     |                                                 |                                          |                                                                                                                                                   |                                                                                                              |                                          |                                                     |                                                            |  |

| (+13h)<br>+2i                                                                               |                                                     |                                                 |                                          | (Not al                                                                                                                                           | lowed)                                                                                                       |                                          |                                                     |                                                            |  |

| (+15h)                                                                                      |                                                     |                                                 |                                          |                                                                                                                                                   |                                                                                                              |                                          |                                                     |                                                            |  |

| +22                                                                                         |                                                     |                                                 |                                          | Status                                                                                                                                            | Reset                                                                                                        |                                          |                                                     |                                                            |  |

| (+16h)                                                                                      | N/A                                                 | N/A                                             | Pacer<br>Clock Error                     | Pacer<br>Clock Input                                                                                                                              | N/A                                                                                                          | N/A                                      | End of<br>Conversion                                | N/A                                                        |  |

|                                                                                             |                                                     |                                                 | CIOCK EITOI                              | Clock Input                                                                                                                                       |                                                                                                              |                                          |                                                     |                                                            |  |

| +23<br>(+17h)                                                                               | (Not allowed)                                       |                                                 |                                          |                                                                                                                                                   |                                                                                                              |                                          |                                                     |                                                            |  |

| (1111)                                                                                      |                                                     |                                                 |                                          | (Not al                                                                                                                                           | lowed)                                                                                                       |                                          |                                                     |                                                            |  |

|                                                                                             |                                                     |                                                 |                                          | `                                                                                                                                                 |                                                                                                              |                                          |                                                     |                                                            |  |

| +24<br>(+18h)                                                                               | C                                                   | C                                               | C                                        | Comma                                                                                                                                             | nd Data                                                                                                      | C                                        | C                                                   | Command                                                    |  |

| +24<br>(+18h)                                                                               | Command<br>Data 07                                  | Command<br>Data 06                              | Command<br>Data 05                       | `                                                                                                                                                 |                                                                                                              | Command<br>Data 02                       | Command<br>Data 01                                  | Command<br>Data 00                                         |  |

| (+18h)                                                                                      |                                                     |                                                 |                                          | Command                                                                                                                                           | nd Data<br>Command                                                                                           |                                          |                                                     |                                                            |  |

| (+18h)                                                                                      |                                                     |                                                 |                                          | Command                                                                                                                                           | nd Data<br>Command<br>Data 03                                                                                |                                          |                                                     |                                                            |  |

| (+18h) +25 (+19h) : +27                                                                     |                                                     |                                                 |                                          | Comma<br>Command<br>Data 04                                                                                                                       | nd Data<br>Command<br>Data 03                                                                                |                                          |                                                     |                                                            |  |

| (+18h)<br>+25<br>(+19h)<br>::<br>+27<br>(+1Bh)                                              |                                                     |                                                 |                                          | Comma<br>Command<br>Data 04                                                                                                                       | nd Data  Command Data 03                                                                                     |                                          |                                                     |                                                            |  |

| (+18h) +25 (+19h) : +27                                                                     | Data 07  Settimg                                    | Data 06  Settimg                                | Data 05                                  | Comma Command Data 04  (Not al                                                                                                                    | nd Data  Command Data 03  lowed)  Data 0  Setting                                                            | Data 02  Settimg                         | Data 01 Settimg                                     | Data 00  Settimg                                           |  |

| (+18h)<br>+25<br>(+19h)<br>:<br>+27<br>(+1Bh)<br>+28<br>(+1Ch)                              | Data 07                                             | Data 06                                         | Data 05                                  | Comma Command Data 04  (Not al  Setting Setting Data 04                                                                                           | nd Data  Command Data 03  lowed)  Data 0  Setting Data 03                                                    | Data 02                                  | Data 01                                             | Data 00                                                    |  |

| (+18h)  +25 (+19h) : +27 (+1Bh) +28                                                         | Settimg<br>Data 07                                  | Settimg<br>Data 06                              | Settimg<br>Data 05                       | Comma Command Data 04  (Not al  Settimg Settimg Data 04  Setting                                                                                  | nd Data  Command Data 03  lowed)  Data 0  Setting Data 03  Data 1                                            | Data 02  Settimg Data 02                 | Data 01  Settimg Data 01                            | Settimg<br>Data 00                                         |  |

| (+18h)  +25 (+19h) : +27 (+1Bh) +28 (+1Ch)                                                  | Data 07  Settimg                                    | Data 06  Settimg                                | Data 05                                  | Comman Command Data 04  (Not al  Setting Setting Data 04  Setting Setting Data 12                                                                 | nd Data Command Data 03  lowed)  Data 0  Setting Data 03  Data 1  Setting Data 11                            | Data 02  Settimg                         | Data 01 Settimg                                     | Data 00  Settimg                                           |  |

| (+18h)<br>+25<br>(+19h)<br>+27<br>(+11Bh)<br>+28<br>(+1Ch)<br>+29<br>(+1Dh)                 | Settimg<br>Data 07<br>Settimg<br>Data 15            | Settimg<br>Data 06<br>Settimg<br>Data 14        | Settimg<br>Data 05<br>Settimg<br>Data 13 | Comma Command Data 04  (Not al  Setting Setting Data 04  Setting Setting Data 12  Setting Setting Setting Setting Setting Setting Setting Setting | Command Data 03  lowed)  Data 0  Setting Data 03  Data 1  Setting Data 11  Setting Data 11  Data 2           | Settimg<br>Data 02<br>Settimg<br>Data 10 | Settimg<br>Data 01                                  | Settimg<br>Data 00                                         |  |

| (+18h) +25 (+19h) : +27 (+1Bh) +28 (+1Ch) +29 (+1Dh)                                        | Settimg<br>Data 07                                  | Settimg Data 06  Settimg Settimg Data 06        | Settimg Data 05  Settimg Data 05         | Comman Command Data 04  (Not al  Setting Setting Data 04  Setting Setting Data 12                                                                 | nd Data Command Data 03  lowed)  Data 0  Setting Data 03  Data 1  Setting Data 11                            | Settimg<br>Data 02                       | Settimg<br>Data 01                                  | Settimg<br>Data 00                                         |  |

| (+18h)<br>+25<br>(+19h)<br>+27<br>(+1Bh)<br>+28<br>(+1Ch)<br>+29<br>(+1Dh)<br>+30<br>(+1Eh) | Settimg<br>Data 07<br>Settimg<br>Data 15<br>Settimg | Settimg<br>Data 06  Settimg<br>Data 14  Settimg | Settimg<br>Data 05<br>Settimg<br>Data 13 | Command Data 04  (Not all Setting Data 04  Setting Data 12  Setting Setting Data 12  Setting Data 12  Setting Data 20                             | command Data 03  lowed)  Settimg Data 03  Setting Data 11  Setting Data 11  Data 2  Setting Data 2           | Settimg<br>Data 02<br>Settimg<br>Data 10 | Settimg<br>Data 01<br>Settimg<br>Data 09<br>Settimg | Settimg Data 00  Settimg Data 00  Settimg Data 08  Settimg |  |

| (+18h)<br>+25<br>(+19h)<br>+27<br>(+11Bh)<br>+28<br>(+1Ch)<br>+29<br>(+1Dh)                 | Settimg<br>Data 07<br>Settimg<br>Data 15<br>Settimg | Settimg<br>Data 06  Settimg<br>Data 14  Settimg | Settimg<br>Data 05<br>Settimg<br>Data 13 | Command Data 04  (Not all Setting Data 04  Setting Data 12  Setting Setting Data 12  Setting Data 12  Setting Data 20                             | nd Data  Command Data 03  lowed)  Data 0  Settimg Data 03  Data 1  Setting Data 11  (Data 2  Setting Data 19 | Settimg<br>Data 02<br>Settimg<br>Data 10 | Settimg<br>Data 01<br>Settimg<br>Data 09<br>Settimg | Settimg Data 00  Settimg Data 00  Settimg Data 08  Settimg |  |

Figure 4.2. Output Port

# **Specifications Common to F&eIT Products**

The regions with starting I/O addresses +0h - +Fh are maps that are common to all modules in the F&eIT series.

### **Product Information**

| Starting<br>I/O Address | D7 | D6      | D5       | D4         | D3                | D2                | D1                | D0                |

|-------------------------|----|---------|----------|------------|-------------------|-------------------|-------------------|-------------------|

| input                   |    | Product | Category |            |                   | Revisio           | n Data            |                   |

| +0<br>(00h)             | 0  | 0       | 1        | 0          | Revision<br>Data3 | Revision<br>Data2 | Revision<br>Data1 | Revision<br>Data0 |

| _                       |    |         |          | Product II | ) Number          |                   |                   |                   |

| +1<br>(01h)             | 0  | 0       | 0        | 0          | 0                 | 0                 | 0                 | 1                 |

Figure 4.3. Product Information

- Revision Data [D3 D0]:

This is product update information, subject to change without notice, that is controlled by CONTEC.

- Product Category [D7 D4]:

This is a module function classification code. For the DAI12-4(FIT)GY, the code is "2h".

Table 4.2. Product Category

| Code  | Function             |

|-------|----------------------|

| 0     | Extention BUS        |

| 1     | Digital input-output |

| 2     | Analog input-output  |

| 3     | Counter              |

| 4     | Serial Communication |

| 5     | GPIB                 |

| 6 - F | Reserved             |

Product ID Number [D7 - D0]:

This is the product ID within the same product category. For the DAI12-4(FIT)GY, ), the product ID is "1h".

Following are examples of the initialization that is performed in high-level languages.

####

\* ADR denotes the starting I/O address for the DAI12-4(FIT)GY.

### **Interrupt Status**

This is a port on which the interrupt status requested by the Module can be verified. Although in this example values are assigned centered on the status concerning interrupt levels, information on interrupt sources varies from module to module.

| I/O Addr    | ess D7 | D6     | D5 | D4       | D3       | D2   | D1   | D0   |

|-------------|--------|--------|----|----------|----------|------|------|------|

| input       |        |        |    | Interrup | t Status |      |      |      |

| +2<br>(02h) | Enable | Status | 0  | 0        | 0        | IRQ9 | IRQ7 | IRQ5 |

### Figure 4.4. Interrupt Status

- Enable [D7]:

This verifies the interrupt source enabled/disabled status.

The value "1" indicates that a hardware interrupt on the controller module is enabled.

- Status [D6]:

This bit indicates an interrupt request status in the module. When IRQ5, IRQ7, or IRQ9 is "1", this bit will also be "1".

- IRQ\* [D2 - D0]:

These bits allow you to verify the interrupt level that is currently set. The current interrupt level is indicated as "1".

Following are examples of the initialization that is performed in high-level languages:

####

### **Setting an Interrupt Level**

| Starting<br>I/O Addre | ess D7 | D6 | D5 | D4      | D3      | D2           | D1           | D0           |

|-----------------------|--------|----|----|---------|---------|--------------|--------------|--------------|

| output                |        |    |    | Interru | pt Data |              |              |              |

| +2<br>(02h)           | Enable | 0  | 0  | 0       | 0       | IRQ9<br>Data | IRQ7<br>Data | IRQ5<br>Data |

### Figure 4.5. Setting an Interrupt Level

- Enable [D7]:

This bit enables an interrupt source.

- IRQ\* [D2 - D0]:

The interrupt level used by the module is set in these bits.

Following are examples of initialization settings that can be effected in high-level languages:

The interrupt level to be used is assigned to IRQ5.

| Microsoft C  |         | Micr | osoft OBA | SIC  |

|--------------|---------|------|-----------|------|

| outp( ADR+2, | 0x81 ); | OUT  | ADR+2,    | &H81 |

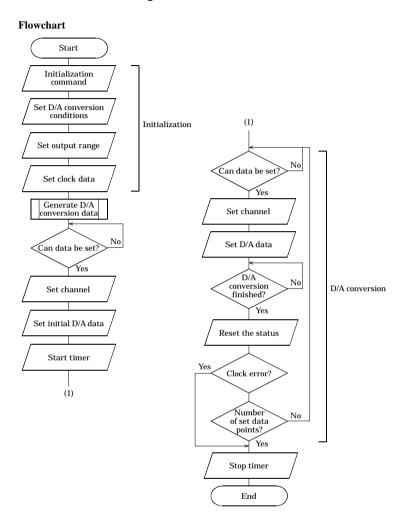

# Overview of the D/A Conversion Function

The analog output function produces specified 12-bit digital data from a specified channel as corresponding voltage or current analog output.

By setting a specific analog output mode, you can specify the method by which the analog output is to be produced.

Two analog output modes are supported:

- -Transparent output mode

- -Synchronous output mode

The transparent output mode updates the analog output from a specified channel immediately after output data is set.

The synchronous output mode pre-sets output data to the channels on which analog output is to be updated, and simultaneously updates analog output from multiple channel when the synchronous output command is issued.

The following chart illustrates the basic conversion process.

Figure 4.6.

Transparent Output Mode

Figure 4.7.

Synchronous Output Mode

### Initialization

This step initializes the analog output function.

This command clears all settings and status, and puts the module in the "initialized status", which is the same as when the power is turned on or RESET button is pressed.

The initialization control port assumes the following state:

| Starting<br>I/O Addre | ess D7 | D6 | D5 | D4   | D3   | D2 | D1 | D0 |

|-----------------------|--------|----|----|------|------|----|----|----|

| output                |        |    |    | Comr | nand |    |    |    |

| +24<br>(18h)          | 0      | 0  | 0  | 0    | 0    | 0  | 0  | 0  |

Figure 4.8. Initialization

Following are examples where the initialization is effected in high-level languages:

| Microsoft C          | Microsoft QBASIC |

|----------------------|------------------|

| outp( ADR+24, 0x0 ); | OUT ADR+24, &H0  |

### Setting D/A Conversion Conditions

This step sets D/A conversion conditions.

In terms of procedures, first a D/A conversion condition setup command is issued, and then setting data is output.

| Starting<br>I/O Addre | ess D7 | D6 | D5 | D4   | D3   | D2 | D1 | D0 |

|-----------------------|--------|----|----|------|------|----|----|----|

| output                |        |    |    | Comi | nand |    |    |    |

| +24<br>(18h)          | 0      | 0  | 0  | 0    | 0    | 0  | 1  | 0  |

|              | D7 | D6 | D5    | D4          | D3           | D2             | D1             | D0                 |

|--------------|----|----|-------|-------------|--------------|----------------|----------------|--------------------|

| output       |    |    | Setti | ng D/A Conv | ersion Condi | itions         |                |                    |

| +28<br>(1Ch) | 0  | 0  | 0     | 0           | 0            | Output<br>Mode | Pacer<br>Clock | Conversion<br>Mode |

Figure 4.9. Setting D/A Conversion Conditions

- Output mode [D2]:

This step sets the specific D/A conversion output method to be employed. Two output methods are available: "transparent mode", in which analog outputs from channels are updated in arbitrary, software-based timing; and "synchronous output mode", in which the analog outputs from multiple channels are simultaneously updated in arbitrary, software-based timing.

Output Mode [0] : Transparent \* Initialized state

[1] : Synchronous output

- Pacer clock [D1]:

This option is set only if the clock mode is selected as a D/A conversion mode.

Pacer Clock [0] : Internal Pacer Clock \* Initialized state

[1] : Reserved

- D/A conversion mode [D0]:

This step sets the timing for D/A conversion output.

Two sampling modes are supported: "software mode", in which analog output is produced from a software-specified channel; and "clock mode", in which periodic D/A conversions are performed by means of clock signals.

Sampling Mode [0] : Software Command \* Initialized state

[1] : Clock

Following are examples in which D/A conversion conditions are specified in high-level languages:

### Microsoft C

### Microsoft OBASIC

### Setting an Output Range

The output range refers to the voltage range over which analog signals are output.

This setting is common to all channels, and involves the conversion of digital signals into analog output signals at a 12-bit resolution level.

The output range setup control port assumes the following state:

| Starting<br>I/O Addres | ss D7 | D6 | D5 | D4   | D3   | D2 | D1 | D0 |

|------------------------|-------|----|----|------|------|----|----|----|

| output                 |       |    |    | Comi | nand |    |    |    |

| +24<br>(18h)           | 0     | 0  | 0  | 0    | 0    | 0  | 1  | 1  |

|                        |       |    |    |      |      |    |    |    |

| output       | D7             | D6             | D5             | D4             | D3             | D2             | D1             | D0             |

|--------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| output       |                |                |                | Range s        | settings       |                |                |                |

| +28<br>(1Ch) | Range<br>Data7 | Range<br>Data6 | Range<br>Data5 | Range<br>Data4 | Range<br>Data3 | Range<br>Data2 | Range<br>Data1 | Range<br>Data0 |

| (1011)       | Dutur          | Dutuo          | Dutuo          | Dutui          | Dutuo          | Dutus          | Dutur          | Dutuo          |

Figure 4.10. Setting an Output Range

Table 4.3. Output Range and Setup Data

| Range         | Output range |

|---------------|--------------|

| 00h           | ±10V         |

| 01h           | ±5V          |

| 02 - 7Fh      | Not decided  |

| 80h           | 0 - 10V      |

| 81h           | 0 - 5V       |

| 82 - BFh      | Undecided    |

| C0h           | 0 - 20mA     |

| C1h and above | Not decided  |

Following are examples in which an output range is specified in high-level languages. The example involves setting an output range of 0 - 10V.

| Microsoft C                 |                   | Microsoft QBASIC                    |

|-----------------------------|-------------------|-------------------------------------|

| outp( ADR+24, outp( ADR+28, | 0x3 );<br>0x80 ); | OUT ADR+24, &H3<br>OUT ADR+28, &H80 |

### Setting an Internal Pacer Clock

When either the "clock mode" or the "internal pacer clock" is selected as a D/A conversion condition, this step specifies a clock cycle (clock data). In the initialized state, the clock data is undefined. When using an internal pacer clock, you must set the requisite clock data.

Clock data is specified in 250-nsec increments.

The allowable range is 10,000nsec - 1,073,741,824,000nsec (approximately 17 minutes 54 seconds), which corresponds to 39 - 4,294,967,295 setup data.

The relationship between clock cycles and setup data can be expressed in the following formula:

$$Clock\ data = \frac{Pacer\ clock}{250}$$

-1

The pacer clock is specified in units of nanoseconds.

The value of the pacer clock must satisfy the following expression:

D/A conversions in accurate cycles cannot be performed if the specified value is less than the conversion time for a specified number of channels.

The internal pacer clock-setting control port assumes the following state:

| Starting     |                  |                  |                  |                  |                  |                  |                  |                  |

|--------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| I/O Addre    | ess D7           | D6               | D5               | D4               | D3               | D2               | D1               | D0               |

| output       |                  |                  |                  | Comr             | nand             |                  |                  |                  |

| +24<br>(18h) | 0                | 0                | 0                | 0                | 0                | 1                | 0                | 0                |

| output       | D7               | D6               | D5               | D4               | D3               | D2               | D1               | D0               |

| output       |                  |                  |                  | Timer            | Data 0           |                  |                  |                  |

| +28<br>(1Ch) | Timer<br>Data 07 | Timer<br>Data 06 | Timer<br>Data 05 | Timer<br>Data 04 | Timer<br>Data 03 | Timer<br>Data 02 | Timer<br>Data 01 | Timer<br>Data 00 |

|              |                  |                  |                  | Timer 1          | Data 1           |                  |                  |                  |

| +29<br>(1Dh) | Timer<br>Data 15 | Timer<br>Data 14 | Timer<br>Data 13 | Timer<br>Data 12 | Timer<br>Data 11 | Timer<br>Data 10 | Timer<br>Data09  | Timer<br>Data08  |

|              |                  |                  |                  | Timer l          | Data 2           |                  |                  |                  |

| +30<br>(1Eh) | Timer<br>Data 23 | Timer<br>Data 22 | Timer<br>Data 21 | Timer<br>Data 20 | Timer<br>Data 19 | Timer<br>Data 18 | Timer<br>Data 17 | Timer<br>Data 16 |

|              |                  |                  |                  | Timer l          | Data 3           |                  |                  |                  |

| +31<br>(1Fh) | Timer<br>Data 31 | Timer<br>Data 30 | Timer<br>Data 29 | Timer<br>Data 28 | Timer<br>Data 27 | Timer<br>Data 26 | Timer<br>Data 25 | Timer<br>Data 24 |

Figure 4.11. Setting an Internal Pacer Clock

Following are examples in which an internal pacer clock is specified in high-level languages:

### Microsoft C Microsoft QBASIC

```

outp( ADR+24, 0x4 ); OUT ADR+24, &H4

outp( ADR+28, ClockData0 ); OUT ADR+28, ClockData0

outp( ADR+29, ClockData1 ); OUT ADR+29, ClockData1

outp( ADR+30, ClockData2 ); OUT ADR+30, ClockData2

outp( ADR+31, ClockData3 ); OUT ADR+31, ClockData3

```

### **Setting a Conversion Channel**

This step specifies the channels from which analog output is to be produced. For byte access, conversion channels should be specified in the following order: channel specification  $\rightarrow$  D/A conversion data (low bytes)  $\rightarrow$  D/A conversion data (high bytes)

| Starting<br>I/O Addre<br>output | ess<br>D7      | D6             | D5  | D4     | D3      | D2                | D1                | D0                |

|---------------------------------|----------------|----------------|-----|--------|---------|-------------------|-------------------|-------------------|

| •                               |                |                |     | Channe | el Data |                   |                   |                   |

| +18<br>(12h)                    | All<br>Channel | End<br>Channel | N/A | N/A    | N/A     | Channel<br>Data 2 | Channel<br>Data 1 | Channel<br>Data 0 |

### Figure 4.12. Setting a Conversion Channel

All channels [D7]:

Assigning the value "1" to this bit causes the D/A conversion data specified in the following step to be output from all channels.

Following are examples in which a conversion channel is specified in high-level languages:

### Microsoft C Microsoft OBASIC

```

outp( ADR+18, 0x80 );

outp( ADR+16, LowerData );

outp( ADR+17, UpperData );

OUT ADR+18, &H80

OUT ADR+16, LowerData

OUT ADR+18, UpperData

```

- Final channel [D6]:

This option is enabled when the synchronous output mode is on.

Assigning the value "1" to this bit specifies the final channel for which the D/A conversion data to be specified in the following step is valid.

Channels for which D/A conversion data can be valid are channels 0 through the final channel.

Following are examples where data is output synchronously from channels 0 and 1:

### Microsoft C

### Microsoft OBASIC

```

outp( ADR+24, 0x2 );

OUT ADR+24, &H2

outp( ADR+28, 0x5 );

OUT ADR+28, &H5

outp( ADR+18, 0x00 );

OUT ADR+18, &H00

outp( ADR+16, LowerData0 );

OUT ADR+18, &H00

outp( ADR+17, UpperData0 );

OUT ADR+17, UpperData0

outp( ADR+18, 0x41 );

OUT ADR+18, &H41

outp( ADR+16, LowerData1 );

OUT ADR+18, &H41

outp( ADR+17, UpperData1 );

OUT ADR+17, UpperData1

```

### **Setting Conversion Data**

Conversion data is specified in offset binary. The relationship between conversion data and analog output is indicated by the following formula:

$$Data = \frac{(voltage + offset)}{span} \times 2^{12}$$

Table 4.4. Output Range

| Output range | Offset | Span |

|--------------|--------|------|

| -10V - +10V  | 10     | 20   |

| -5V - +5V    | 5      | 10   |

| 0V - +10V    | 0      | 10   |

| 0V - +5V     | 0      | 5    |

| 0mA - +20mA  | 0      | 20   |

-10.000V

Table 4.5. Example of Conversion Data over a ±10V Range

:

0000 h

| Starting<br>I/O Addro<br>output | ess<br>D7                  | D6                  | D5                   | D4<br>Chann          | D3<br>el Data             | D2                   | D1                   | D0                       |

|---------------------------------|----------------------------|---------------------|----------------------|----------------------|---------------------------|----------------------|----------------------|--------------------------|

| +18<br>(12h)                    | All<br>Channel             | End<br>Channel      | N/A                  | N/A                  | N/A                       | Channel<br>Data 02   | Channel<br>Data 01   | Channel<br>Data 00       |

|                                 |                            |                     |                      |                      |                           |                      |                      |                          |

| output                          | D7                         | D6                  | D5                   | D4                   | D3                        | D2                   | D1                   | D0                       |

| •                               | Analog output Data (Lower) |                     |                      |                      |                           |                      |                      |                          |

| +16<br>(10h)                    | Conversion<br>Data7        | Conversion<br>Data6 | Conversion<br>Data5  | Conversion<br>Data4  | Conversion<br>Data3       | Conversion<br>Data2  | Conversion<br>Data1  | Conversion<br>Data0(LSB) |

|                                 |                            |                     | A                    | nalog output         | Data (Uppe                | r)                   |                      |                          |

| +17<br>(11h)                    | 0                          | 0                   | 0                    | 0                    | Conversion<br>Data11(MSB) | Conversion<br>Data10 | Conversion<br>Data9  | Conversion<br>Data8      |

| input                           | D7                         | D6                  | D5                   | D4                   | D3                        | D2                   | D1                   | D0                       |

| put                             |                            |                     |                      | Analog Out           | put Status                | -                    |                      |                          |

| +22<br>(16h)                    | 0                          | 0                   | Pacer<br>Clock Error | Pacer<br>Clock Input | 0                         | 0                    | End of<br>Conversion | Data Set<br>Busy         |

Figure 4.13. Output Port for Setting Conversion Data

The channel/conversion data output control procedure is described below.

Details on analog output and the interrupt status is given in the following section.

Following are examples in which a D/A conversion process is started in high-level languages.

Following are examples in which conversion data is output in high-level languages:

| Microsoft C                                          | Microsoft QBASIC                                    |

|------------------------------------------------------|-----------------------------------------------------|

| while(inp(ADR+22 &1));<br>outp(ADR+18, 0x0);         | WHILE(INP((ADR+22)AND1)=1): WEND<br>OUT ADR+18, &HO |

| outp(ADR+16, LowerData);<br>outp(ADR+17, UpperData); |                                                     |

## **Details on the Analog Output Status**

The analog output status indicates the status of the D/A conversion operation.

| Starting<br>I/O Addre | ess D7               | D6 | D5                   | D4                   | D3 | D2 | D1                   | D0               |

|-----------------------|----------------------|----|----------------------|----------------------|----|----|----------------------|------------------|

| input                 | D7                   | D0 | D3                   |                      |    | Di | D1                   |                  |

|                       | Analog Output Status |    |                      |                      |    |    |                      |                  |

| +22<br>(16h)          | 0                    | 0  | Pacer<br>Clock Error | Pacer<br>Clock Input | 0  | 0  | End of<br>Conversion | Data Set<br>Busy |

|                       |                      |    |                      |                      |    |    |                      |                  |

| output                | D7                   | D6 | D5                   | D4                   | D3 | D2 | D1                   | D0               |

| output                | Status Reset         |    |                      |                      |    |    |                      |                  |

| +22<br>(16h)          | 0                    | 0  | Pacer<br>Clock Error | Pacer<br>Clock Input | 0  | 0  | End of<br>Conversion | 0                |

Figure 4.14. Analog Output Status

### Dataset Busy (DSB) [D0]:

When this bit is [0], the dataset is available for the output of D/A conversion data. When this bit is [1], the dataset is writing data to a D/A converter register in the module and is unavailable for writing any other D/A conversion data.

### End of Conversion (EOC) [D2]:

When [1] is set to this status bit, the data that has been written to the D/A converter is converted into analog signals. This bit is cleared when [1] is set to the End of Conversion Status of the analog output status reset port.

The end of conversion does not include analog signal setup time. \*

### Pacer Clock Input Status [D4]:

[1] is set to this status bit when a pacer clock is input after the timer start command is issued in the clock mode. This bit is cleared when [1] is set to the clock input status bit for the analog output status reset port. \*

### Pacer Clock Error Status [D5]:

[1] is set to this status bit when a pacer clock is re-entered with the pacer clock input status bit being [1], during the operation of the timer in the clock mode.

This bit is cleared when [1] is set to the pacer clock error status bit for the analog output status reset port. \*

- \* These status bits are also [0] cleared under the following conditions:

- -When the initialization command is issued

- -When the D/A conversion condition-setting command is issued

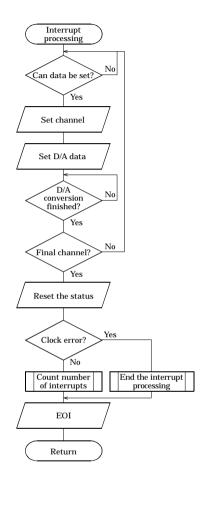

### **Interrupt Function**

This option allows you to use the hardware interrupt function.

For interrupt levels, a level that is set by the Module will be used.

When using the interrupt function, you can pre-select one of the following status conditions as an interrupt source (multiple settings allowed):

**Table 4.6.** Interrupt Function

| Status            | Explanation                                                          |  |  |  |  |

|-------------------|----------------------------------------------------------------------|--|--|--|--|

| End of Conversion | When the writing of conversion data to the D/A converter is finished |  |  |  |  |

| Pacer Clock Input | When a pacer clock is input                                          |  |  |  |  |

| Pacer Clock Error | When the pacer clock error status is set                             |  |  |  |  |

An interrupt request signal is generated simultaneously with the setting of the status that is specified as an interrupt source. If two or more interrupt sources are specified, you can specify a specific interrupt signal generation source by entering a status in the interrupt handler.

### **Setting an Interrupt Source**

This option allows you to specify an interrupt signal generation source.

Pacer Pacer Clock Error Clock Input

The control port that sets an interrupt source assumes the following state:

| Starting<br>I/O Addre |                  |    |    |    |    |    |    |    |

|-----------------------|------------------|----|----|----|----|----|----|----|

| output                | ess D7           | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| Command               |                  |    |    |    |    |    |    |    |

| +24<br>(18h)          | 0                | 0  | 0  | 0  | 0  | 0  | 0  | 1  |