# DATA SHEET

## **Industrial CompactFlash Card**

## AC31-XXXX-XXX1 AC31-XXXX-XXX2

POWER QUOTIENT INTERNATIONAL CO.,LTD. 14F, No.16, Jian Ba Road Chung Ho City, Taipei, Taiwan, R.O.C.

Tel: +886-2-8226-5288, Fax: +886-2-8226-3689

Web site: www.pqi.com.tw

| Approved   | Design      |  |  |

|------------|-------------|--|--|

| Alex Chien | Peter Huang |  |  |

## Contents~

| 1. Description           | 3  |

|--------------------------|----|

| 2. Features              | 3  |

| 3. Interface Description | 4  |

| 3.1 Card pin Assignment  |    |

| 3.2 Card pin Description |    |

| 3.3 Block Diagram        |    |

| 4. Physical outline      | 10 |

## 1. Description

AC31-XXXX is **CompactFlash™** based on TDK GBDriver flash memory controller technology. This card complies with **CompactFlash™** specification, it is suitable for the usage of data storage memory for PC or other electric equipment and digital still camera. This card is equipped with NAND flash memory. By using this card it is possible to operate stability for the system that have **CompactFlash™** slots.

Fixed mode (045A)~AC31-XXXX-XXX2 disk use in system storage, some operating system can not accept boot-up from removable mode (848A)~AC31-XXXX-XXX1 disk like windows XP, when we boot-up from CFC with windows XP, the system detect the device will disable Removable device boot-up function, so the system can not finish the boot-up process. For this issue, we can setting the device mode to Fixed mode (045A) to solve this problem.

The CFC setting to Fixed or Removable mode will no any function different or issue.

#### **2.** Features

- 32Mbytes~2Gbytes flash memory card.

- CompactFlash™ specification: PCMCIA ver.2.1 and PC Card ATA ver.2.01 compatible 50pin SMT connector and type I (3.3mm).

- 3.3V/5V single power supply operation.

- Internal self-diagnostic program operates at VCC power on.

- 3 variations of access mode:

- Memory Card Mode.

- I/O Card Mode.

- True-IDE Mode.

- High reliability based on internal ECC (Error Correcting Code) Function.

- Data reliability is 1 error in 10<sup>14</sup> bits read.

- Temperature range: 0 to +70

- MTBF: 1,000,000 hours.

- Endurance: 2,000,000 erase/program cycles

- Power Consumption (3.3V/ 5.0V).

- Active mode: 24.1mA/ 26.5mA (3.3v/ 5.0v).

- Sleep mode: 200 uA / 300 uA (3.3v/ 5.0v).

- High Performance:

- Read: 4.0Mbytes/s.(32Mbytes~64Mbytes), 4.1Mbytes/s.(128Mbytes~2Gbytes)

- Write: 1.5Mbytes/s.(32Mbytes~64Mbytes), 3.5Mbytes/s.(128Mbytes~2Gbytes)

Notes: The performance will depend on different platform with different test result.

## 3. Interface Description

### 3.1 Card pin Assignment

|          | Memory car  | I/O card n | I/O card mode |            | True IDE mode   |              |  |

|----------|-------------|------------|---------------|------------|-----------------|--------------|--|

| Pin NO.  | Signal name | I/O        | Signal name   | I/O        | Signal name I/O |              |  |

| 1        | GND         |            | GND           | 1/0        | GND             | 1/0          |  |

| -        | D3          | I/O        | D3            | I/O        | D3              | I/O          |  |

| 3        | D3          | I/O        | D3            | 1/0        | D3              | 1/0          |  |

| 4        | D5          | I/O        | D5            | 1/0        | D5              | 1/0          |  |

| 5        | D6          | I/O        | D6            | I/O        | D6              | 1/0          |  |

| 6        | D7          | I/O        | D7            | I/O        | D7              | 1/0          |  |

| 7        | -CE1        | I          | -CE1          | 1/0        | -CE1            | 1/0          |  |

|          | A10         | <u> </u>   | A10           | l<br>I     | A10             |              |  |

| 8        |             | <u> </u>   |               |            |                 | !            |  |

| 9        | -OE         | <u> </u>   | -OE           | <u> </u>   | -ATASEL         |              |  |

| 10       | A9          | <u> </u>   | A9            |            | A9              |              |  |

| 11       | A8          |            | A8            |            | A8              |              |  |

| 12       | A7          |            | A7            |            | A7              |              |  |

| 13       | VCC         | -          | VCC           | -          | VCC             | -            |  |

| 14       | A6          | I          | A6            |            | A6              |              |  |

| 15       | A5          | j          | A5            | i          | A5              | i            |  |

| 16       | A4          | i          | A4            | i          | A4              | i            |  |

| 17       | A3          | <u> </u>   | A3            |            | A3              | i            |  |

| 18       | A2          | <u> </u>   | A3<br>A2      | l<br>I     | A2              | <u> </u>     |  |

|          |             | <u> </u>   |               | l I        |                 |              |  |

| 19       | A1          | <u> </u>   | A1            | <u> </u>   | A1              |              |  |

| 20       | A0          |            | A0            |            | A0              |              |  |

| 21       | D0          | I/O        | D0            | I/O        | D0              | I/O          |  |

| 22       | D1          | I/O        | D1            | I/O        | D1              | I/O          |  |

| 23       | D2          | I/O        | D2            | I/O        | D2              | I/O          |  |

| 24       | WP          | 0          | -IOIS16       | 0          | -IOIS16         | 0            |  |

| 25       | -CD2        | 0          | -CD2          | 0          | -CD2            | 0            |  |

| 26       | -CD1        | 0          | -CD1          | 0          | -CD1            | 0            |  |

| 27       | D11<br>D12  | I/O<br>I/O | D11<br>D12    | I/O<br>I/O | D11<br>D12      | I/O<br>I/O   |  |

| 28<br>29 | D12         | I/O        | D12           | 1/0        | D12             | 1/0          |  |

| 30       | D13         | I/O        | D13           | 1/0        | D13             | 1/0          |  |

| 31       | D15         | I/O        | D15           | I/O        | D15             | 1/0          |  |

| 32       | -CE2        | I          | -CE2          | 1/0        | -CE2            | 1/0          |  |

| 33       | -VS1        | 0          | -VS1          | 0          | -VS1            | 0            |  |

| 34       | -IORD       | <u> </u>   | -IORD         | i O        | -IORD           | Ī            |  |

| 35       |             | <u> </u>   |               | <u> </u>   | -IORD<br>-IOWR  |              |  |

|          | -IOWR       | <u> </u>   | -IOWR         | l<br>I     |                 |              |  |

| 36       | -WE         | <u> </u>   | -WE           | <u> </u>   | -WE             |              |  |

| 37       | RDY/-BSY    | 0          | -IREQ         | 0          | INTRQ           | 0            |  |

| 38       | VCC         |            | VCC           | _          | VCC             | <del>-</del> |  |

| 39       | -CSEL       | <u> </u>   | -CSEL         | ļ          | -CSEL           |              |  |

| 40       | -VS2        | 0          | -VS2          | 0          | -VS2            | 0            |  |

| 41       | RESET       |            | RESET         |            | -RESET          |              |  |

| 42       | -WAIT       | 0          | -WAIT         | 0          | IORDY           | 0            |  |

| 43       | -INPACK     | 0          | -INPACK       | 0          | -INPACK         | 0            |  |

| 44       | -REG        | 1          | -REG          |            | -REG            |              |  |

| 45       | BVD2        | 1/0        | -SPKR         | I/O        | -DASP           | I/O          |  |

| 46       | BVD1        | I/O        | -STSCHG       | 1/0        | -PDIAG          | I/O          |  |

| 47       | D8          | I/O        | D8            | I/O        | D8              | I/O          |  |

| 48       | D9          | I/O        | D9            | I/O        | D9              | I/O          |  |

| 49       | D10         | I/O        | D10           | I/O        | D10             | I/O          |  |

| 50       | GND         | _          | GND           | _          | GND             | _            |  |

### 3.2 Card pin Description

| Signal Name                                                               | Dir | Pin No.                         | Description                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                               |  |  |

|---------------------------------------------------------------------------|-----|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| A10 to A0<br>(PC Card Memory<br>Mode)  A10 to A0<br>(PC Card I/O<br>Mode) | -   | 8,10,11,12,14,15,16,17,18,19,20 | These address lines along with the-REG signal are used to select the following: The I/O port address registers within the CompactFlash Storage Card or CF + Card, the memory mapped port add address registers within the CompactFlash Storage Card or CF+ Card, a byte in the card's information structure and its configuration control and status registers. |                                                                                                                                               |  |  |

| A2 to A0<br>(True IDE Mode)                                               |     | 18,19,20                        | In True IDE Mode only A {2:0} are used to select the one of eight registers in the Task File. The remaining address lines should be grounded by the host.                                                                                                                                                                                                       |                                                                                                                                               |  |  |

| BVD1<br>(PC Card Memory<br>Mode)                                          | I/O |                                 |                                                                                                                                                                                                                                                                                                                                                                 | This signal is asserted high as BVD1 is not supported                                                                                         |  |  |

| -STSCHG<br>(PC Card Memory<br>Mode)                                       |     | 46                              | This signal is asserted low to alert the host to changes in the RDY/-BSY and Write Protect states; while the I/O interface is configured. Its use is controlled by the Card Configured and Status Register.                                                                                                                                                     |                                                                                                                                               |  |  |

| -PDIAG<br>(True IDE Mode)                                                 |     |                                 | In the True IDE Mode, this input/output is the Pass Diagnostic signal in the Master/Slave handshake protocol.                                                                                                                                                                                                                                                   |                                                                                                                                               |  |  |

| BVD2<br>(PC Card Memory<br>Mode)                                          | I/O |                                 | This signal is asserted high, as BVD2 is not supported.                                                                                                                                                                                                                                                                                                         |                                                                                                                                               |  |  |

| -SPKR<br>(PC Card / I/O<br>Mode)                                          |     | I/O                             | 45                                                                                                                                                                                                                                                                                                                                                              | This line is the Binary AUDIO OUTPUT FROM THE CARD .if the Card does not support the Binary Audio function, this line should be held negated. |  |  |

| -DASP<br>(True IDE Mode)                                                  |     |                                 | In the True IDE Mode, this input/output is the Disk Active/Slave Present signal in the Master/Slave                                                                                                                                                                                                                                                             |                                                                                                                                               |  |  |

| -CD1,-CD2<br>(PC Card Memory<br>Mode)                                     | 0   | 26,25                           | These Card Detect pins are connected to ground on the CompcatFlash Storage Card or CF + Card. They are used by the host to determine that the CompactFlash Storage Card or CF + Card is fully inserted into its socket.                                                                                                                                         |                                                                                                                                               |  |  |

| -CE1,-CE2<br>(PC Card I/O<br>Mode)<br>-CE1,-CE2<br>(PC Card I/O<br>Mode)  | -   | 7,32                            | These input signals are used both to select the card and to indicate to the card whether a byte or a word operation is being performed. –CE2 always accesses the odd byte of the word depending on A0 and –CE2. A multiplexing scheme based on A1CE1,-CE2 allows 8 bit hosts to access all data on D0 to D7.                                                    |                                                                                                                                               |  |  |

| -CS0,-CS1<br>(True IDE Mode)                                              |     |                                 | See Access specification below.  In the True IDE Mode CS0 is the chip select for the task file registers while CS1 is used to select the Alternate Status Register and the Device Control Register.                                                                                                                                                             |                                                                                                                                               |  |  |

| -CSEL<br>(PC Card Memory<br>Mode                                          |     |                                 | This signal is not used for this mode.                                                                                                                                                                                                                                                                                                                          |                                                                                                                                               |  |  |

| -CSEL<br>(PC Card I/O<br>Mode)                                            | I   | 39                              | This internally pulled up signal is used to configure this device as a Master or a Slave when configured in the True IDE Mode. When this pin is grounded, this device is configured as a Master.                                                                                                                                                                |                                                                                                                                               |  |  |

| -CSEL<br>(True IDE Mode)                                                  |     |                                 | When the pins is open, this device is configured as a Master.  a Slave.                                                                                                                                                                                                                                                                                         |                                                                                                                                               |  |  |

| Signal Name                                                                   | Dir | Pin No.                                   | Description                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------|-----|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D15 to D00<br>(PC Card Memory<br>Mode)<br>D15 to D00<br>(PC Card I/O<br>Mode) | I/O | 31,30,29,28,27,49,48,47,6,5,4,3,223,22,21 | These lines carry the Data, Commands and Status information between the host and the controller.D00 is the LSB of the Even Byte of the Word.D08 is the LSB of the Even Byte of the Word.D08 is the LSB of the Odd Byte of the Word.                                                                                                           |

| D15 to D00<br>(True IDE Mode)                                                 | =   |                                           | True IDE Mode, all Task File operations occur in byte mode on the low order bus D00 to D07 while all data transfers are 16 bit using D00 to D15.                                                                                                                                                                                              |

| GND (PC Card Memory Mode) GND (PC Card I/O Mode) GND                          | _   | 1,50                                      | Ground                                                                                                                                                                                                                                                                                                                                        |

| -INPCAK<br>(PC Card Memory<br>Mode)                                           |     |                                           | This signal is not used in this mode.                                                                                                                                                                                                                                                                                                         |

| -INPACK<br>(PC Card I/O<br>Mode)                                              | 0   | 43                                        | The Input Acknowledge signal is asserted by the CompactFlash Storage Card or CF +Card when the card is selected and responding to an I/O read cycle at the address that is on the address bus. This signal is used by the host to control the enable of any input data buffers between the CompactFlash Storage Card or CF +Card and the CPU. |

| -INPACK<br>(True IDE Mode)                                                    |     |                                           | In True IDE Mode this output signal is not used and should not be connected at the host.                                                                                                                                                                                                                                                      |

| -IORD<br>(PC Card Memory<br>Mode)                                             |     |                                           | This signal is not used in this mode.                                                                                                                                                                                                                                                                                                         |

| -IORD<br>(PC Card I/O<br>Mode)                                                | I   | 34                                        | This is an I/O Read strobe generated by the host. This signal gates I/O data onto the bus from the CompactFlash Storage Card or CF +Card when the card is configured to use the I/O interface.                                                                                                                                                |

| -IORD<br>(True IDE Mode)                                                      |     |                                           | In True IDE Mode, this signal has same function as in PC Card I/O Mode.                                                                                                                                                                                                                                                                       |

| -IOWR<br>(PC Card Memory<br>Mode)                                             |     |                                           | This signal is not used in this mode.                                                                                                                                                                                                                                                                                                         |

| -IOWR<br>(PC Card I/O<br>Mode)                                                | I   | 35                                        | The I/O Write strobe pulse is used to clock I/O data on the Card Data bus into the CompcatFlash Storage Card or CF +Card controller registers when the CompactFlash Storage Card or CF +Card is configured to use the I/O interface. The clocking will occur on the negative to positive edge of the signal (Trailing edge)                   |

| -IOWR<br>(True IDE Mode)                                                      |     |                                           | In True IDE Mode, this signal has the same function as in PC Card I/O Mode.                                                                                                                                                                                                                                                                   |

| Signal Name                                                         | Dir    | Pin No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------|--------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -OE<br>(PC Card Memory<br>Mode)                                     |        |         | This is an Output Enable strobe generated by the host interface. It is used to read data from the CompactFlash Storage Card or CF +Card in Memory Mode and to read the CIS and configuration registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| -OE<br>(PC Card I/O<br>Mode)                                        | I      | 9       | In PC Card I/O Mode. This signal is used to read the CIS and configuration registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| -ATA SEL<br>(True IDE Mode)                                         |        |         | To enable True IDE Mode this input should be grounded by the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RDY/BSY<br>(PC Card Memory<br>Mode)                                 | 0      | 37      | In Memory Mode this signal is set high when the CompactFlash Storage Card or CF +Card is ready to accept a new data transfer operation and held low when the card is busy. The Host memory card socket must provide a pull-up resistor. At power up and at Reset the RDY/-BSY signal is held low (busy) until the CompactFlash Storage Card or CF +Card has completed its power up or reset function. No access of any type should be made to the CompactFlash Storage Card or CF +Card during this time. The RDY/-BSY signal is held high (disabled from being busy) whenever the following condition is true. The CompactFlash Storage Card or CF +Card has been powered up with + RESET continuously disconnected or asserted. |

| -IREQ<br>(PC Card I/O<br>Mode)                                      |        |         | Operation-After the CompactFlash Storage Card or CF + Card has been configured for I/O operation; this signal is used as interrupt Request. This line is strobe low to generate a pulse mode interrupt or held low for a level mode interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| INTRQ<br>(True IDE Mode)                                            |        |         | In True IDE Mode signal is the active high interrupt Request to the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| -REG<br>(PC Card Memory<br>Mode)                                    |        |         | This signal is used during Memory Cycles to distinguish between Common Memory and Register(Attribute) Memory accesses. High for Common Memory. Low for Attribute Memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| -REG<br>(PC Card I/O<br>Mode)                                       | I      | 44      | The signal must also be active (low) during I/O Cycles when the I/O address is on the Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| -REG<br>(True IDE Mode)                                             |        |         | In the True IDE Mode this input pin is the active low hardware reset from the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RESET<br>(PC Card Memory<br>Mode)<br>RESET<br>(PC Card I/O<br>Mode) | -<br>I | 41      | When the pin is high, this signal Resets the CompactFlash Storage Card or CF +Card. The CompcatFlash Storage Card or CF +Card is Reset only at power up if this pin is left high or open from power-up. The CompactFlash Storage Card or CF +Card is also Reset when the Soft Reset bit in the Card Configuration Option Register is set.                                                                                                                                                                                                                                                                                                                                                                                         |

| -RESET<br>(True IDE Mode)                                           |        |         | In the True IDE Mode this input pin is the active low hardware reset form the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Signal Name                                                                        | Dir | Pin No. | Description                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC<br>(PC Card Memory<br>Mode)<br>(PC Card I/O<br>Mode)<br>(True IDE Mode)        | _   | 13,38   | +5V +3.3V power.                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                              |

| -VS1 /-VS2<br>(PC Card Memory<br>Mode)<br>(PC Card I/O<br>Mode)<br>(True IDE Mode) | 0   | 33,40   | Voltage Sense Signals. –VS1 is grounded so that the CompactFlash Storage Card or CF + Card CIS can be read at 3.3 volts and –VS2 is reserved by PCMCIA for a secondary voltage.                                                                                              |                                                                                                                                                                                                                                                              |

| -WAIT<br>(PC Card Memory<br>Mode)                                                  | 0   | 42      | The –WAIT signal is driven low by the CompactFlash Storage Card or CF +Card to signal the host to delay completion of a memory or I/O cycle that is in progress.                                                                                                             |                                                                                                                                                                                                                                                              |

| IORDY<br>(True IDE Mode)                                                           |     |         | In True IDE Mode this output signal may be used as IORDY                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                              |

| -WE<br>(PC Card Memory<br>Mode)                                                    | - 1 |         |                                                                                                                                                                                                                                                                              | This is a signal driven by the host and used for starting memory write data to the registers of the CompactFlash Storage Card or CF + Card when the card is configured I the memory interface mode. It is also used for writing the configuration registers. |

| -WE<br>(PC Card I/O<br>Mode)                                                       |     | 36      | In PC Card I/O Mode, this signal is used for writing the configuration registers.                                                                                                                                                                                            |                                                                                                                                                                                                                                                              |

| -WE<br>(True IDE Mode)                                                             |     |         | In True IDE Mode this input signal is not used and should be connected to VCC by the host.                                                                                                                                                                                   |                                                                                                                                                                                                                                                              |

| WP<br>(PC Card Memory<br>Mode)                                                     |     |         | Memory Mode-The CompactFlash Storage Card or CF + Card does not have a write protect switch. This signal is held low after the completion of the reset initialization sequence.                                                                                              |                                                                                                                                                                                                                                                              |

| -IOIS16<br>(PC Card I/O<br>Mode)                                                   | 0   | 24      | I/O Operation-When the CompactFlash Storage Card or CF + Card is configured for I/O Operation Pin 24 is used for the –I/O Selected is 16 Bit Port (-IOIS16)function. A Low signal indicates that a 16 bit or odd byte only operation can be performed at the addressed port. |                                                                                                                                                                                                                                                              |

| -IOIS16<br>(True IDE Mode)                                                         |     |         | In True IDE Mode this output signal is asserted low when this device is expecting a word data transfer cycle.                                                                                                                                                                |                                                                                                                                                                                                                                                              |

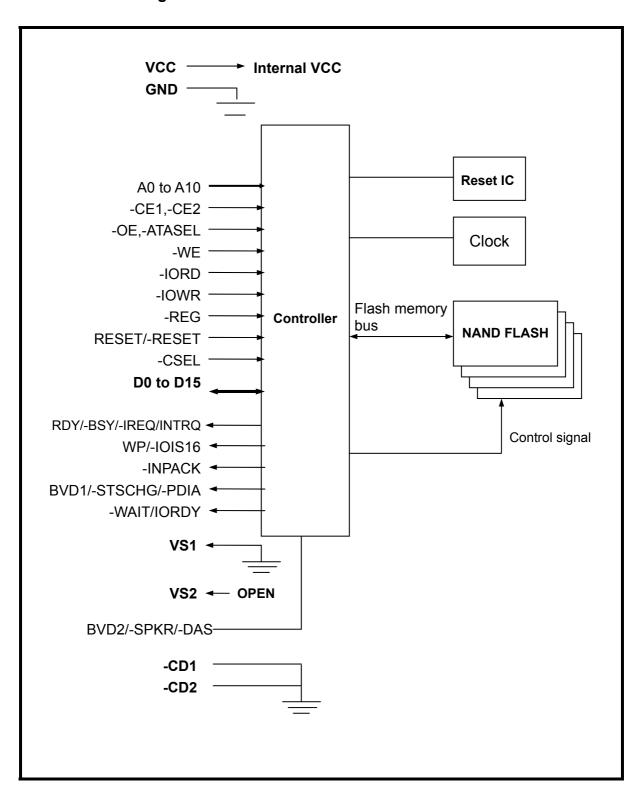

#### 3.3 Card Block Diagram

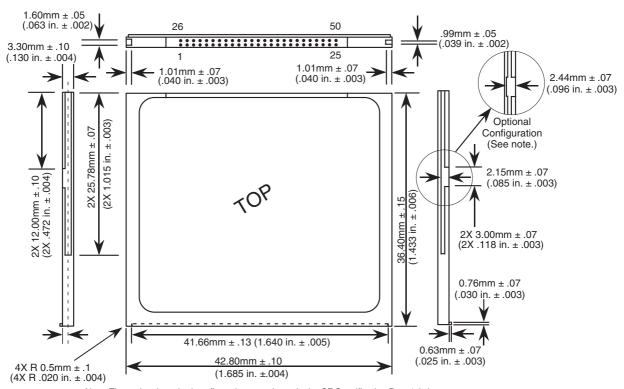

## 4. Physical outline

Note: The optional notched configuration was shown in the CF Specification Rev. 1.0. In specification Rev. 1.2, the notch was removed for ease of tooling. This optional configuration can be used but it is not recommended.