# PXIe-3975

# **User's Manual**

Manual Rev.:

2.00

Revision Date:

Dec 29, 2011

Part No: 50-17035-1000

# Advance Technologies; Automate the World.

# **Revision History**

| Revision | Release Date | Description of Change(s) |  |

|----------|--------------|--------------------------|--|

| 2.00     | 2011/12/29   | Initial Release          |  |

# Preface

# Copyright 2011 ADLINK TECHNOLOGY INC.

This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of the manufacturer.

## Disclaimer

The information in this document is subject to change without prior notice in order to improve reliability, design, and function and does not represent a commitment on the part of the manufacturer.

In no event will the manufacturer be liable for direct, indirect, special, incidental, or consequential damages arising out of the use or inability to use the product or documentation, even if advised of the possibility of such damages.

#### **Environmental Responsibility**

ADLINK is committed to fulfill its social responsibility to global environmental preservation through compliance with the European Union's Restriction of Hazardous Substances (RoHS) directive and Waste Electrical and Electronic Equipment (WEEE) directive. Environmental protection is a top priority for ADLINK. We have enforced measures to ensure that our products, manufacturing processes, components, and raw materials have as little impact on the environment as possible. When products are at their end of life, our customers are encouraged to dispose of them in accordance with the product disposal and/or recovery programs prescribed by their nation or company.

#### Trademarks

PC, PS/2, and VGA are registered trademarks of International Business Machines Corp. Borland<sup>®</sup>, Borland<sup>®</sup> C, C++ Builder<sup>®</sup>, and Delphi<sup>®</sup> are registered trademarks of the Borland Software Corporation. LabVIEW<sup>TM</sup> is a trademark of National Instruments Corporation. Microsoft<sup>®</sup>, Visual Basic<sup>®</sup>, Visual C++<sup>®</sup>, Windows<sup>®</sup>

98, Windows<sup>®</sup> NT, Windows<sup>®</sup> 2000, Windows<sup>®</sup> XP, and Windows<sup>®</sup> Vista<sup>®</sup> are registered trademarks of Microsoft<sup>®</sup> Corporation. PCI<sup>™</sup>, is a registered trademark of the Peripheral Component Interconnect Special Interest Group (PCI-SIG).

Product names mentioned herein are used for identification purposes only and may be trademarks and/or registered trademarks of their respective companies.

#### Conventions

Take note of the following conventions used throughout this manual to make sure that users perform certain tasks and instructions properly.

Additional information, aids, and tips that help users perform tasks.

Information to prevent *minor* physical injury, component damage, data loss, and/or program corruption when trying to complete a task.

Information to prevent *serious* physical injury, component damage, data loss, and/or program corruption when trying to complete a specific task.

# **Table of Contents**

| R  | evisio             | on His | ioryii                             |

|----|--------------------|--------|------------------------------------|

| Pı | eface              | )      | iii                                |

| Li | st of I            | Figur  | əs ix                              |

| Li | st of <sup>·</sup> | Table  | s xi                               |

| 1  | Intro              | ducti  | on 1                               |

|    | 1.1                | Featu  | ıres 2                             |

|    | 1.2                | Spec   | ifications                         |

| 2  | Gett               | ing St | arted 7                            |

|    | 2.1                | Pack   | age Contents 7                     |

|    | 2.2                | Oper   | ating System Installation 8        |

|    | 2.3                | Hard   | ware Instructions                  |

|    | 2.                 | 3.1    | Faceplate Connectors & Indicators9 |

|    | 2.                 | 3.2    | PXI Trigger Connector 10           |

|    | 2.                 | 3.3    | DVI-I Connector 11                 |

|    | 2.                 | 3.4    | GPIB Connector                     |

|    | 2.                 | 3.5    | Reset Button 13                    |

|    | 2.                 | 3.6    | LED Indicators                     |

|    | 2.                 | 3.7    | USB 2.0 Ports                      |

|    | 2.                 | 3.8    | Gigabit Ethernet Ports15           |

|    | 2.                 | 3.9    | ExpressCard/3416                   |

|    | 2.                 | 3.10   | Onboard Connections and Settings17 |

|    | 2.                 | 3.11   | Installation Environment18         |

|    | 2.                 | 3.12   | Installing the PXIe-3975 19        |

|    | 2.                 | 3.13   | Replacing the Hard Drive 20        |

|    | 2.                 | 3.14   | Replacing the Battery Backup21     |

|    | 2.                 | 3.15   | Clearing CMOS Jumper (JP1)24       |

| 3 | Driv | er Ins | tallation                            | 25 |

|---|------|--------|--------------------------------------|----|

|   | 3.1  | Insta  | lling Windows Drivers                | 25 |

|   | 3.2  | Insta  | lling the Chipset Driver             | 25 |

|   | 3.3  | Insta  | Iling the Graphics Driver            | 26 |

|   | 3.4  | Insta  | Iling the Ethernet Driver            | 27 |

|   | 3.5  | Insta  | lling the GPIB Driver                | 27 |

|   | 3.6  | Insta  | lling the Management Engine Driver   | 28 |

|   | 3.7  | Insta  | Iling the PXI Trigger Driver         | 28 |

|   | 3.8  | Insta  | lling the WDT Driver                 | 28 |

| 4 | BIO  | S Seti | q.                                   | 31 |

|   | 4.1  | Start  | ing the BIOS                         | 31 |

|   | 4.2  | Main   | Setup                                | 33 |

|   | 4.3  | Adva   | nced Setup                           | 34 |

|   | 4.4  | Chips  | set Configuration                    | 35 |

|   | 4.5  | Boot   | Setup                                | 35 |

|   | 4.6  | Secu   | rity Setup                           | 36 |

|   | 4.7  | Save   | e & Exit Setup                       | 36 |

| Α | Арр  | endix  | : PXI Trigger I/O Function Reference | 39 |

|   | A.1  | Data   | Types                                | 39 |

|   | A.2  | Func   | tion Library                         | 40 |

|   | А    | .2.1   | TRIG_Init                            | 40 |

|   | Α    | .2.2   | TRIG_Close                           | 41 |

|   | Α    | .2.3   | TRIG_SetSoftTrg                      | 41 |

|   | Α    | .2.4   | TRIG_Trigger_Route                   | 42 |

|   | A    | .2.5   | TRIG_Trigger_Clear                   | 44 |

|   | A    | .2.6   | TRIG_GetSoftTrg                      | 45 |

|   | A    | .2.7   | TRIG_Trigger_Route_Query             | 46 |

|   | Α    | .2.8   | TRIG_GetDriverRevision               | 48 |

|   | Α    | .2.9   | CONTROLLER_GetHwRevision             | 49 |

|   | Α    | .2.10  | CONTROLLER_GetManufacturer           | 50 |

|    | A.2.11          | CONTROLLER_GetModel        | 51 |  |  |

|----|-----------------|----------------------------|----|--|--|

|    | A.2.12          | CONTROLLER_GetSerialNumber | 51 |  |  |

| в  | Appendix:       | Watchdog Timer             | 53 |  |  |

|    | B.1 WDT         | Function Library           | 53 |  |  |

|    | B.1.1           | InitWDT                    | 53 |  |  |

|    | B.1.2           | SetWDT                     | 54 |  |  |

|    | B.1.3           | StartWDT                   | 55 |  |  |

|    | B.1.4           | ResetWDT                   | 55 |  |  |

|    | B.1.5           | StopWDT                    | 56 |  |  |

| Im | portant Sa      | fety Instructions          | 57 |  |  |

| G  | Getting Service |                            |    |  |  |

This page intentionally left blank.

# **List of Figures**

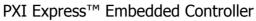

| Figure 1-1: | PXIe-3975 Functional Block Diagram | 3  |

|-------------|------------------------------------|----|

| Figure 2-1: | PXIe-3975 Faceplate                |    |

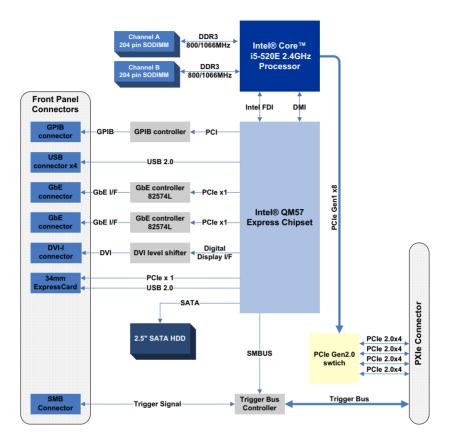

| Figure 2-2: | PXI Trigger SMB Jack               | 10 |

| Figure 2-3: | PXIe-3975 LED Indicators           | 13 |

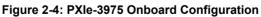

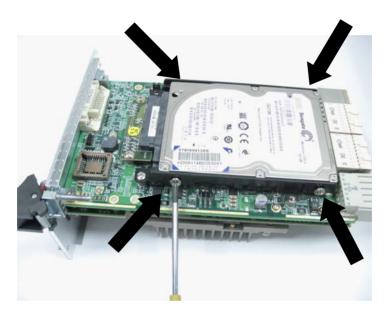

| Figure 2-4: | PXIe-3975 Onboard Configuration    | 17 |

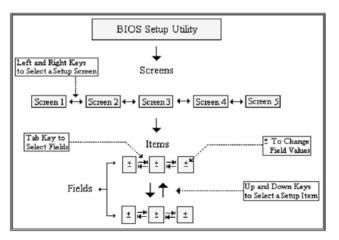

| Figure 4-1: | BIOS Setup Navigation              | 32 |

This page intentionally left blank.

# List of Tables

| 2-1: | DVI-I Pin Assignment                                                         | 11                                           |

|------|------------------------------------------------------------------------------|----------------------------------------------|

| 2-2: | GPIB Pin Description                                                         | 12                                           |

| 2-3: | LED Indicator Legend                                                         | 13                                           |

| 2-4: | USB 2.0 Port Pin Assignment                                                  | 14                                           |

| 2-5: | PXIe-3975 Ethernet Port Pin Assignments                                      | 15                                           |

| 4-1: | BIOS Hot Key Functions                                                       | 32                                           |

| 4-2: | BIOS Main Setup Menu                                                         | 33                                           |

| 4-3: | BIOS Advanced Setup Menu                                                     | 34                                           |

| 4-4: | BIOS Chipset Configuration Menu                                              | 35                                           |

| 4-5: | BIOS Boot Setup Menu                                                         | 35                                           |

| 4-6: | BIOS Security Setup Menu                                                     |                                              |

|      | 2-2:<br>2-3:<br>2-4:<br>2-5:<br>4-1:<br>4-2:<br>4-2:<br>4-3:<br>4-4:<br>4-5: | <ul> <li>2-1: DVI-I Pin Assignment</li></ul> |

This page intentionally left blank.

# 1 Introduction

The ADLINK PXIe-3975 PXI Express<sup>™</sup> embedded controller, based on the Intel<sup>®</sup> Core<sup>™</sup> i5 processor, is specifically designed for PXI Express-based testing systems, providing a rugged and stable operating environment for a wide variety of testing and measurement applications.

Combining state-of-the-art Intel<sup>®</sup> Core<sup>TM</sup> i5-520E 2.4 GHz processors, and up to 8 GB of 1066 MHz DDR3 memory, the PXIe-3975 utilizes two separate computing engines on a single processor, enabling execution of two independent tasks simultaneously in a multi-tasking environment. With a configurable PCIe switch, the PXIe-3975 can support four links x4 or two links x8 PXI Express link capability, with maximum system throughput of up to 2 GB/s.

PXI Express-based testing systems typically make up a PXI Express platform and diversified standalone instruments for complex testing tasks. The PXIe-3975 provides ample interface choices, including GPIB, USB, and ExpressCard, for connecting and controlling instruments. The PXIe-3975 series also provides dual Gigabit Ethernet ports, one for LAN connection and the other for controlling LXI instruments. With flexible instrument control interfaces and mechanical and electronic reliability, the ADLINK PXIe-3975 is more than equal to the challenges of the most demanding PXIe-based testing systems.

8GB memory addressing is OS-dependent, such that a 32-bit operating system may be unable to address the full 8GB of memory space. To fully utilize the 8GB memory, 64-bit operating systems are required.

# 1.1 Features

- ▶ PXI<sup>™</sup>-5 PXI Express Hardware Specification Rev.1.0

- Intel<sup>®</sup> Core<sup>™</sup> i5-520E 2.4 GHz processor for maximum computing power

- ► Dual Channel DDR3 SODIMM

- ▷ Up to 8 GB 1066 MHz

- Maximum System Throughput 2 GB/s

- ► PXI Express Link Capability

- ▷ Four Link Configuration: x4 x4 x4 x4

- ▷ Two Link Configuration: x8 x8

- ▶ Pre-installed SATA hard drive at 160 GB, 7200 RPM

- ▷ Supports 2.5" HDD or SSD

- ▷ SATA 3.0 Gb/s

- ▷ Supports AHCI

- Integrated I/O

- Dual Gigabit Ethernet ports

- ▷ Four USB 2.0 Ports

- ▷ Built-in GPIB (IEEE488) controller

- DVI-I video connector

- ExpressCard/34 expansion slot

- ▷ Trigger I/O for advanced PXI<sup>™</sup> trigger functions

- ▶ Programmable watchdog timer

# 1.2 Specifications

Figure 1-1: PXIe-3975 Functional Block Diagram

#### Processor

- ▶ Intel<sup>®</sup> Core<sup>™</sup> i5-520E 2.4GHz processor

- DMI (Direct Media Interface) with 1 GB/s of bandwidth in each direction

## Chipset

Mobile Intel<sup>®</sup> QM57 Express

#### Memory

- ► Two standard 204-pin DDR3 SODIMM sockets

- Support for +1.5 V DDR3, 800/1066 MHz RAM up to 8 GB total

- ► Support for non-ECC unbuffered memory

#### Video

- ▶ DVI output supporting up to 1920x 1200 @ 60 Hz resolution

- CRT output for analog CRT route to DVI-I connector on the faceplate, supporting up to 2048 x 1536 bpp at 75Hz

- DVI-I connector for both digital and analog video signal output

# Hard Drive

Built-in 2.5" 160 GB SATA hard drive, 7200 RPM

## I/O Connectivity

Dual Gigabit Ethernet controllers through two RJ-45 connectors with speed/link/active LED on the faceplate, with upper connector supporting Wake on LAN.

#### USB

Four USB 2.0 ports on the faceplate.

## GPIB

Onboard IEEE488 GPIB controller through Micro-D 25-pin connector on the faceplate.

#### ExpressCard/34

34mm wide ExpressCard expansion slot

## Trigger I/O

One SMB connector on the faceplate to route an external trigger signal to/from PXI trigger bus

## Dimensions (3-slot 3U PXIe module)

3U/3-slot PXI/Compact PCI standard 60.5 W x 128.7 H x 213.2 D mm (2.38 x 5.07 x 8.39 in.)

## **Slot Requirements**

System slot and 2 controller expansion slots

## Weight

0.9 kg (exclusive of packaging)

#### Environmental

Operating temperature 0 to 55°C Storage temperature -20 to 70°C Relative humidity 5 to 95%, non-condensing

#### Shock and Vibration

Functional shock 30 G, half-sine, 11 ms pulse duration Random vibration:

- ▶ Operating 5 to 500 Hz, 0.21 Grms, 3 axes

- ▶ Non-operating 5 to 500 Hz, 2.46 Grms, 3 axes

## Certification

Electromagnetic compatibility:

- ► EMC/EMI: CE, FCC Class A

- ▶ CE Compliance EN 61326-1

The PXIe-3975 meets the essential requirements of applicable European Directives.

# **Power Requirements**

| Voltage rail              | 5 V standby | 3.3 V  | 5 V    | 12 V   |

|---------------------------|-------------|--------|--------|--------|

| Maximum power consumption | 0.12 A      | 0.75 A | 0.76 A | 2.81 A |

| Typical power consumption | 0.11 A      | 0.72 A | 0.54 A | 0.9 A  |

# 2 Getting Started

This chapter describes procedures for installing the PXIe-3975 and making preparations for its operation, including hardware and software setup. Please note that the PXIe-3975 is shipped with RAM and HDD pre-installed. Please contact ADLINK or authorized dealer if there are any problems during the installation.

Diagrams and illustrated equipment are for reference only. Actual system configuration and specifications may vary.

# 2.1 Package Contents

Before beginning, check the package contents for any damage and ensure that the following items are included:

- ► PXIe-3975 Controller (equipped with RAM and HDD)

- DVI-to-VGA adapter

- ▶ PXIe-3975 User's Manual

- ► ADLINK All-In-One CD

If any of these items are missing or damaged, contact the dealer from whom you purchased the product. Save the shipping materials and carton in case you want to ship or store the product in the future.

Do not install or apply power to equipment that is damaged or missing components. Retain the shipping carton and packing materials for inspection. Please contact your ADLINK dealer/ vendor immediately for assistance and obtain authorization before returning any product.

## 2.2 Operating System Installation

For more detailed information about the operating system, refer to the documentation provided by the operating system manufacturer. Preferred/supported operating systems for PXIe-3975 are:

- Windows XP

- ▶ Windows 7 32/64bits

- ► For other OS support, please contact ADLINK

Most operating systems require initial installation from a hard drive, floppy drive, or CD-ROM drive. The PXIe-3975 controller supports USB CD-ROM drive, USB flash disk, USB external hard drive, or a USB floppy drive as the first boot device. Please see Section 4.5: Boot Setup for information about setting the boot devices. These devices should be configured, installed, and tested with the supplied drivers before attempting to load the new operating system.

Read the release notes and installation documentation provided by the operating system vendor. Be sure to read all the README files or documents provided on the distribution disks, as these typically note documentation discrepancies or compatibility problems.

- Select the appropriate boot device order from the BIOS Boot Setup Menu based on the OS installation media used. For example, if the OS is distributed on a bootable installation CD, select USB CD-ROM as the first boot device and reboot the system with the installation CD in the USB CD-ROM drive

- Proceed with the OS installation as directed and be sure to select appropriate device types if prompted. Refer to the appropriate hardware manuals for specific device types and compatibility modes of ADLINK PXI products.

- 3. When installation is complete, reboot the system and set the boot device order in the SETUP boot menu accordingly.

# 2.3 Hardware Instructions

#### 2.3.1 Faceplate Connectors & Indicators

Figure 2-1: PXIe-3975 Faceplate

| A | PXI Trigger Connector<br>(SMB jack) | E | LED indicators              |

|---|-------------------------------------|---|-----------------------------|

| В | DVI-I Connector                     | F | 4X Type-A USB<br>connectors |

| С | GPIB Connector<br>(Micro D-Sub 25P) | G | 2X Gigabit Ethernet         |

| D | Reset Button                        | н | ExpressCard/34              |

# 2.3.2 PXI Trigger Connector

Figure 2-2: PXI Trigger SMB Jack

The PXI trigger connector is a SMB jack, used to route external trigger signals to or from the PXI backplane. Trigger signals are TTL-compatible and edge sensitive. The PXIe-3975 provides four trigger routing modes from/to the PXI trigger connector to synchronize PXI modules, including

- ▶ From a selected trigger bus line to PXI trigger connector

- ► From the PXI trigger connector to a selected trigger bus line

- ► From software trigger to a selected trigger bus line

- ► From software trigger to PXI trigger connector

All trigger modes are programmable by the provided driver. Please refer to Section A: PXI Trigger I/O Function Reference for further information.

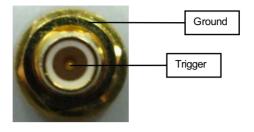

#### 2.3.3 DVI-I Connector

The DVI-I connector connects the PXIe-3975 to a monitor, of which both digital (DVI) and analog (VGA) are supported. If connecting to an analog (VGA) monitor, the included DVI-to-VGA adapter must be installed on the DVI-I connector.

| Pin | Signal           | Pin | Signal             | Pin | Signal           | Pin | Signal           |

|-----|------------------|-----|--------------------|-----|------------------|-----|------------------|

| 1   | TMDS<br>Data2-   | 9   | TMDS<br>Data1-     | 17  | TMDS<br>Data0-   | C1  | Analog<br>Red    |

| 2   | TMDS<br>Data2+   | 10  | TMDS<br>Data1+     | 18  | TMDS<br>Data0+   | C2  | Analog<br>Green  |

| 3   | Shield<br>Ground | 11  | Shield<br>Ground   | 19  | Shield<br>Ground | C3  | Analog<br>Blue   |

| 4   | Reserved         | 12  | Reserved           | 20  | Reserved         | C4  | Analog<br>HSYNC  |

| 5   | Reserved         | 13  | Reserved           | 21  | Reserved         | C5  | Analog<br>Ground |

| 6   | DDC Clock        | 14  | +5V Power          | 22  | Ground           |     |                  |

| 7   | DDC Data         | 15  | Ground             | 23  | TMDS<br>Clock+   |     |                  |

| 8   | Analog<br>VSYNC  | 16  | Hot Plug<br>Detect | 24  | TMDS<br>Clock-   |     |                  |

Table 2-1: DVI-I Pin Assignment

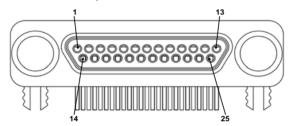

#### 2.3.4 GPIB Connector

The GPIB connector on PXIe-3975 is a micro D-sub 25P connector, controlling external bench-top instruments. Connection to other instruments requires the ACL-IEEE488-MD1-A cable. The on-board GPIB controller provides:

- ► Full compatibility with IEEE 488 standard

- ▶ Up to 1.5MB/s data transfer rates

- Onboard 2 KB FIFO for read/write operations

- ▶ Driver APIs compatible with NI-488.2 driver software

- ► Connection with up to 14 instruments

| Pin | Signal            | Description           | Pin | Signal | Description   |

|-----|-------------------|-----------------------|-----|--------|---------------|

| 1   | DIO1#             | GPIB Data 1           | 14  | DIO5#  | GPIB Data 5   |

| 2   | DIO2#             | GPIB Data 2           | 15  | DIO6#  | GPIB Data 6   |

| 3   | DIO3#             | GPIB Data 3           | 16  | DIO7#  | GPIB Data 7   |

| 4   | DIO4#             | GPIB Data 4           | 17  | DIO8#  | GPIB Data 8   |

| 5   | EOI               | End Or Identify       | 18  | REN    | Remote Enable |

| 6   | DAV               | Data Valid            | 19  | Ground | Signal Ground |

| 7   | NRFD              | Not Ready For<br>Data | 20  | Ground | Signal Ground |

| 8   | NDAC              | No Data Accepted      | 21  | Ground | Signal Ground |

| 9   | IFC               | Interface Clear       | 22  | Ground | Signal Ground |

| 10  | SRQ               | Service Request       | 23  | Ground | Signal Ground |

| 11  | ATN               | Attention             | 24  | Ground | Signal Ground |

| 12  | Chassis<br>Ground | Chassis Ground        | 25  | Ground | Signal Ground |

| 13  | Ground            | Signal Ground         |     |        |               |

| Table | 2-2: | GPIB | Pin | Description |

|-------|------|------|-----|-------------|

|-------|------|------|-----|-------------|

#### 2.3.5 Reset Button

The reset button, activated by insertion of any pin-like implement, executes a hard reset for the PXIe-3975.

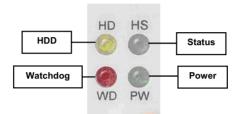

# 2.3.6 LED Indicators

Four LED indicators on the faceplate indicate operational status of the PXIe-3975, as follows.

| LED<br>indicator | Color  | Description                                                                                                                                                                 |

|------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power LED        | Green  | Indicates system power. Remains lit when the system boots normally and main power supply is functioning.                                                                    |

| HDD LED          | Yellow | Indicates operating state of the HDD. Flashes during access to or activity on the SATA HDD.                                                                                 |

| Watchdog         | Red    | Indicates status of the watchdog timer, lighting<br>when watchdog timer has expired. Please refer<br>to Appendix B for watchdog timer programming<br>information.           |

| HS LED           | Blue   | Indicates system status, blinking on and off once<br>during boot when system status is good, and<br>continuously blinking or remaining lit when the<br>system malfunctions. |

| Table | 2-3: | LED | Indicator | Legend |

|-------|------|-----|-----------|--------|

|-------|------|-----|-----------|--------|

In the event of malfunction, clear the CMOS (please see Section 2.3.15: Clearing CMOS Jumper (JP1)) and reboot the system. If the system fails to respond properly, please contact ADLINK for assistance.

# 2.3.7 USB 2.0 Ports

The PXIe-3975 provides four USB 2.0 ports via USB Type A connectors on the faceplate, all compatible with hi-speed, full-speed and low-speed USB devices. Supported boot devices include USB flash drive, USB floppy, USB CD-ROM, and others, with boot priority and device settings configurable configured in BIOS. Please see Section 4.5: Boot Setup for more information.

| Pin | Signal     |

|-----|------------|

| 1/5 | Power 5V   |

| 2/6 | USB Data-  |

| 3/7 | USB Data + |

| 4/8 | Ground     |

Table 2-4: USB 2.0 Port Pin Assignment

#### 2.3.8 Gigabit Ethernet Ports

Two Intel 82574L GbE controllers via x1 PCI Express interface provide dual Gigabit Ethernet connectivity, with the upper connector supporting Wake-on-LAN function.

| Pin | 1000Base-T Signal | 100/10Base-T Signal |

|-----|-------------------|---------------------|

| 1   | MDI0+             | TX+                 |

| 2   | MDI0-             | TX-                 |

| 3   | MDI1+             | RX+                 |

| 4   | MDI2+             | Reserved            |

| 5   | MDI2-             | Reserved            |

| 6   | MDI1-             | RX-                 |

| 7   | MDI3+             | Reserved            |

| 8   | MDI3-             | Reserved            |

Table 2-5: PXIe-3975 Ethernet Port Pin Assignments

The Ethernet ports each include two LED indicators, one Active/ Link indicator and one Speed indicator, functioning as follows.

|   | LED                         | Status   | Description                                               |

|---|-----------------------------|----------|-----------------------------------------------------------|

|   | Active/Link<br>(Yellow)     | Off      | Ethernet port is disconnected                             |

|   |                             | ON       | Ethernet port is connected with no data transmission      |

| E |                             | Flashing | Ethernet port is connected with data transmitted/received |

|   | Speed<br>(Green/<br>Orange) | Off      | 10 Mbps                                                   |

|   |                             | Green    | 100 Mbps                                                  |

|   |                             | Orange   | 1000 Mbps                                                 |

Although the port 2 Intel 82574 Ethernet device remains powered even after shutdown and the Active/Link LED may remain blinking, it is safe to remove the controller or disconnect power.

#### 2.3.9 ExpressCard/34

The PXIe-3975 controller is equipped with an ExpressCard/34 slot on the front panel, which provides I/O expansion. ExpressCard connector signals are as follows.

| Pin | Signal   | Description             | Pin | Signal  | Description           |

|-----|----------|-------------------------|-----|---------|-----------------------|

| 1   | GND      | Ground                  | 14  | +3.3V   | Power                 |

| 2   | USBD-    | USB Data -              | 15  | +3.3V   | Power                 |

| 3   | USBD+    | USB Data +              | 16  | CLKREQ# | Clock Request         |

| 4   | CPUSB#   | USB Presence            | 17  | CPPE#   | PE Presence           |

| 5   | RESERVED | Reserved for future use | 18  | REFCLK- | Reference<br>Clock-   |

| 6   | RESERVED | Reserved for future use | 19  | REFCLK+ | Reference<br>Clock+   |

| 7   | SMBCLK   | SMBus Clock             | 20  | GND     | Ground                |

| 8   | SMBDATA  | SMBus Data              | 21  | PERn0   | PE Data<br>Receive -  |

| 9   | +1.5V    | Power                   | 22  | PERp0   | PE Data<br>Receive +  |

| 10  | +1.5V    | Power                   | 23  | GND     | Ground                |

| 11  | WAKE#    | PE Wake                 | 24  | PETn0   | PE Data<br>Transmit - |

| 12  | +3,3VAUX | Power                   | 25  | PETp0   | PE Data<br>Transmit + |

| 13  | PERST#   | PE Reset                | 26  | GND     | Ground                |

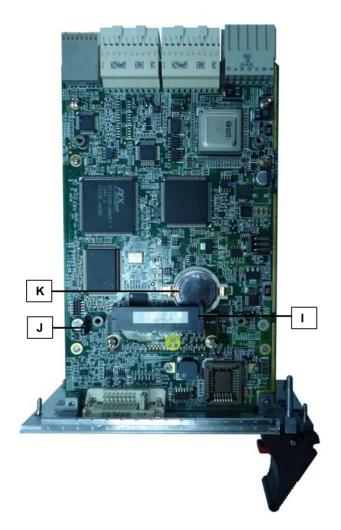

## 2.3.10 Onboard Connections and Settings

| I | SATA Connector |

|---|----------------|

| J | JP1 (CMOS)     |

| К | System Battery |

While the PXIe-3975 ships with a 2.5" SATA hard drive pre-installed to the SATA port, no HDD is shown installed, for clarity.

# 2.3.11 Installation Environment

When preparing to install any equipment described in this manual, please refer to Chapter C: Important Safety Instructions.

Only install equipment in well lit areas on flat, sturdy surfaces with access to basic tools such as flat- and cross-head screwdrivers, preferably with magnetic heads as screws and standoffs are small and easily misplaced.

**Recommended Installation Tools**

Phillips (cross-head) screwdriver

Flat-head screwdriver

Anti-static wrist strap

Anti-static mat

ADLINK PXIe-3975 system controllers are electrostatically sensitive and can be easily damaged by static electricity. The equipment must be handled on a grounded anti-static mat, and operators must wear an anti-static wristband, grounded at the same point as the anti-static mat.

Inspect the carton and packaging for damage. Shipping and handling may cause damage to the contents. Ensure that all contents are undamaged before installing.

All equipment must be protected from static discharge and physical shock. Never remove any of the socketed parts except at a static-free workstation. Use the antistatic bag shipped with the product to handle the equipment and wear a grounded wrist strap when servicing or installing.

#### 2.3.12 Installing the PXIe-3975

- 1. Locate the system controller slot (Slot 1)

- 2. Depress the red locking lever and release the latch

- 3. Align the controller's top and bottom edges with the card guides, and carefully slide the PXIe-3975 into the chassis, as shown

- 4. Elevate the latch until the PXIe-3975 is fully seated in the chassis backplane.

- 5. Fasten the four mounting screws on the faceplate of PXIe-3975, and connect all peripheral devices.

#### 2.3.13 Replacing the Hard Drive

The PXIe-3975 provides a SATA 2.0 port with a pre-installed 2.5" SATA hard drive. Alternatively, a 2.5" solid state disk (SSD) can be used for shock/vibration resistance. This section explains procedures for replacing the HDD.

- 1. Locate the four screws attaching the hard drive to the bracket on the rear of the PXIe-3975 controller.

- 2. Remove the screws, as shown.

3. Gently lift and remove the SATA hard drive, as shown, being careful to not bend or break the SATA Board-to-Board connector.

4. To replace the HD with a solid state hard drive or other compatible SATA hard drive, reverse the steps and reinstall the PXIe-3975 to the PXI system.

## 2.3.14 Replacing the Battery Backup

The PXIe-3975 is provided with a 3.0 V "coin cell" lithium battery. To replace the battery, proceed as follows.

- 1. Turn off the PXIe chassis.

- 2. Remove the PXIe-3975 embedded controller from the chassis. Observe all anti-static precautions.

- 3. Locate the four screws attaching the hard drive to the bracket on the rear of the PXIe-3975 controller.

- 4. Remove the screws, as shown.

- Gently lift and remove the SATA hard drive, being careful to not bend or break the SATA Board-to-Board connector.

- 6. The battery backup is exposed.

- To remove the battery, gently insert a small (approx. 5 mm) flat-head screwdriver under the battery at the negative retaining clip. Gently pry the battery up, again, being careful of the SATA connector. The battery should easily pop out.

- Place a fresh identical battery (CR2032 or equivalent) in the socket, ensuring that the positive pole (+) is facing upwards. The battery is most easily seated by first being inserted under the positive retaining clip, and then

pushed downward at the negative retaining clip. The battery should easily snap into position.

- 9. Replace the hard drive.

- 10.Reinstall the embedded controller into the PXIe chassis and restore power.

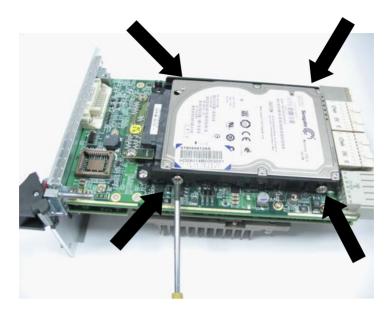

### 2.3.15 Clearing CMOS Jumper (JP1)

In the event of a system malfunction causing the PXIe-3975 to halt or fail to boot, clear the CMOS and restore the controller BIOS to its default settings. To clear the CMOS:

- 1. Shut down the controller operating system. Turn off the PXIe Chassis.

- 2. Remove the PXIe-3975 from the chassis. Observe all anti-static precautions.

- 3. Locate the JP1 jumper on the board. Move the jumper from Normal to Clear (short pin#2 and pin#3), as shown.

- 4. Remount the controller into the PXIe chassis.

- 5. Power on the chassis and immediately depress the Reset button on the faceplate, before any monitor display appears.

- 6. After the operating system starts, shut down the controller operating system and power down the PXIe chassis.

- 7. Once again, remove the PXIe-3975 controller from the chassis.

- 8. Restore jumper JP1 to the Normal position (short pin#1 and pin#2).

- 9. Remount the controller into the PXIe chassis and restore power.

# 3 Driver Installation

After installing the operating system, all related drivers must be installed for correct system operation. This section describes drivers needed for Windows operating systems and the procedures to install them. For other OS support, please contact ADLINK.

# 3.1 Installing Windows Drivers

- 1. Fully install Windows, which contains most standard I/O device drivers

- 2. Install the chipset driver

- 3. Install the graphic driver

- 4. Install the Ethernet driver

- 5. Install the GPIB driver

- 6. Install the management engine driver

- 7. Install the PXI trigger driver

- 8. Install the WDT (watchdog timer) driver

# 3.2 Installing the Chipset Driver

This section describes installation of the chipset driver for PXIe-3975. The chipset driver directs the operating system to configure the Intel® QM57 chipset components to ensure operation of:

- ► Core PCI and ISAPNP Services

- ► PCle Support

- SATA Storage Support

- ▶ USB Support

- Identification of Intel® Chipset Components in the Device Manager

To install the chipset driver:

- 1. Close any running applications

- 2. Insert the ADLINK All-in-One CD (x: denotes the CD-ROM drive)

- Driver Installation\PXI Platform\PXI Controller\PXIe-3975\Chipset\WinXP\INF\_Update\_Utility

- The Win7 chipset driver is located in the directory x:\ Driver Installation\PXI Platform\PXI Controller\PXIe-3975\Chipset\Win7\INF\_Update\_Utility

- 3. Execute infinst911autol.exe and follow on-screen instructions to complete the setup

- 4. Reboot the system

# 3.3 Installing the Graphics Driver

To install the graphics driver:

- 1. Close any running applications

- 2. Insert the ADLINK All-in-One CD (x: denotes the CD-ROM drive)

- The WinXP VGA driver is located in the directory x:\ Driver Installation\PXI Platform\PXI controller\PXIe-3975\VGA\WinXP\32Bits

- The 32bit Win7 VGA driver is located in the directory x:\ Driver Installation\PXI Platform\PXI controller\PXIe-3975\VGA\Win7\32Bits

- The 64bit Win7 VGA driver is located in the directory x:\ Driver Installation\PXI Platform\PXI controller\PXIe-3975\VGA\Win7\64Bits

- 3. Execute setup.exe and follow on-screen instructions to complete the setup

- 4. Reboot the system

# 3.4 Installing the Ethernet Driver

To install the Ethernet driver:

- 1. Close any running applications.

- 2. Insert the ADLINK All-in-One CD (x: denotes the CD-ROM drive)

- The WinXP Ethernet driver is located in the directory: x:\ Driver Installation\PXI Platform\PXI controller\PXIe-3975\LAN\WinXP\32Bits\

- The 32bit Win7 Ethernet driver is located in the directory x:\ Driver Installation\PXI Platform\PXI controller\PXIe-3975\LAN\Win7\32Bits\

- The 64bit Win7 Ethernet driver is located in the directory x:\ Driver Installation\PXI Platform\PXI controller\PXIe-3975\LAN\Win7\64Bits\

- 3. Execute PROWin32.exe or PROWin64x.exe and follow on-screen instructions to complete the setup.

- 4. Reboot the system

# 3.5 Installing the GPIB Driver

The PXI-3975 controller features an onboard GPIB controller, providing connectivity between PXI and GPIB instruments. The GPIB driver package also contains function libraries and a utility to interact with GPIB instruments.

To install the GPIB driver:

- 1. Close any running applications.

- Insert the ADLINK All-in-One CD (x: denotes the CD-ROM drive); the GPIB driver is located in the directory x:\ Driver Installation\PXI Platform\PXI controller\PXIe-3975\GPIB\

- 3. Execute setup.exe and follow on-screen instructions to complete the setup

- 4. Reboot the system

# 3.6 Installing the Management Engine Driver

To install the management engine driver:

- 1. Close any running applications.

- 2. Insert the ADLINK All-in-One CD (x: denotes the CD-ROM drive)

- The WinXP ME driver is located in the directory x:\ Driver Installation\PXI Platform\PXI controller\PXIe-3975\ME\WinXP\Intel ME

- The Win7 ME driver is located in the directory x:\ Driver Installation\PXI Platform\PXI controller\PXIe-3975\ME\Win7\Intel ME

- 3. Execute MEI\_ALLOS\_6.1.0.1042\_PV.exe or setup.exe and follow on-screen instructions to complete the setup.

- 4. Reboot the system

# 3.7 Installing the PXI Trigger Driver

The PXIe-3975 controller provides a trigger I/O on the faceplate to route the trigger signal to and from the PXI trigger bus. Please see Appendix A: PXI Trigger I/O Function Reference for programming information.

To install the PXI trigger driver:

- 1. Close any running applications.

- Insert the ADLINK All-in-One CD (x: denotes the CD-ROM drive); the PXI trigger driver is located in the directory x:\ Driver Installation\PXI Platform\PXI controller\PXIe-3975\PXI\_Trigger\ PXI Trigger 3.23

- 3. Execute **PXI Trigger IO setup v323.exe** and follow onscreen instructions to complete the setup

- 4. Reboot the system

# 3.8 Installing the WDT Driver

The WDT (watchdog timer) resets the system when the operating system or application is halted. The WDT typically starts and periodically resets the timer, and when the timer is expired, the system

resets. Please refer to Appendix B: Watchdog Timer for programming information.

To install the WDT driver:

- 1. Close any running applications.

- 2. Insert the ADLINK All-in-One CD (x: denotes the CD-ROM drive); the WDT driver is located in the directory x:\ Driver Installation\PXI Platform\PXI controller\PXIe-3975\PXI\_WDT\ PXI WDT 3.23

- 3. Execute **PXI WDT Setup v323.exe** and follow on-screen instructions to complete the setup

- 4. Reboot the system

This page intentionally left blank.

# 4 BIOS Setup

The Basic Input/Output System (BIOS) provides a basic level of communication between the processor and peripherals. In addition, the BIOS also contains code for various advanced features applied to the PXIe-3975 controller. The BIOS setup program includes menus for configuring settings and enabling PXIe-3975 controller features.

Changing BIOS settings may result in incorrect operation and possibly an inability to boot. If this occurs, follow the instructions in Section 2.3.15: Clearing CMOS Jumper (JP1) to clear CMOS and restore default settings. In general, do not change a BIOS setting unless you are absolutely certain of the consequences.

# 4.1 Starting the BIOS

- 1. Power on or reboot the PXIe-3975 controller.

- Press the <Delete> key when the controller beeps. This should be concurrent with the main startup screen. The BIOS setup program loads after a short delay.

- 3. The Main menu is displayed when you first enter the BIOS setup program.

In most cases, the < Delete > key is used to invoke the setup screen. There are several cases that use other keys, such as < F1 >, < F2 >, and so on.

The main BIOS setup menu is the first screen that you can navigate. Each main BIOS setup menu option is described in this user's guide.

The Main BIOS setup menu screen has two main frames. The left frame displays all the options that can be configured. "Grayed" options cannot be configured, "Blue" options can be.

The right frame displays the key legend. Above the key legend is an area reserved for a text message. When an option is selected in the left frame, it is highlighted in white. Often a text message will accompany it.

# Navigation

The BIOS setup/utility uses a key-based navigation system called hot keys. Most BIOS setup utility hot keys can be used at any time during setup navigation, as follows.

| Key(s)                  | Function                                                                                  |

|-------------------------|-------------------------------------------------------------------------------------------|

| Right Arrow, Left Arrow | Moves between different setup menus                                                       |

| Up Arrow, Down Arrow    | Moves between options within a setup menu                                                 |

| <enter></enter>         | Opens a submenu or displays all available settings for a highlighted configuration option |

| <esc></esc>             | Returns to the previous menu and shortcuts to the Exit menu from top-level menus          |

| <+> and <>              | Cycles between all available settings                                                     |

| <tab></tab>             | Selects time and date fields                                                              |

| <f1></f1>               | Opens the general help window for the BIOS                                                |

| <f2></f2>               | Loads previous values into the BIOS                                                       |

| <f3></f3>               | Restores default values into the BIOS                                                     |

| <f4></f4>               | Saves the current configuration and exits BIOS setup                                      |

| <f9></f9>               | Loads the optimal default BIOS settings                                                   |

Table 4-1: BIOS Hot Key Functions

A hot key legend is located in the right frame on most setup screens.

The < F8 > key on your keyboard is the Fail-Safe key. It is not displayed on the key legend by default. To set the Fail-Safe settings of the BIOS, press the < F8 > key on your keyboard. It is located on the upper row of a standard 101 keyboard. The Fail-Safe settings allow the motherboard to boot up with the least amount of options set. This can lessen the probability of conflicting settings.

# 4.2 Main Setup

When you first enter the Setup Utility, you will enter the Main setup screen. You can always return to the Main setup screen by selecting the Main tab.

The Main Setup menu provides basic controller information and allows the system time and date to be set, as follows.

| Item               | Detail                                                          |

|--------------------|-----------------------------------------------------------------|

| BIOS Information   | Includes BIOS version and the date on which the BIOS was built  |

| Memory Information | Shows memory size, type and speed as detected by the BIOS       |

| ME Information     | Indicates the version of the management engine                  |

| Board Information  | Such as hardware revisions and serial number                    |

| System Date & Time |                                                                 |

| System Date        | Changes system date, date must be entered in<br>MM/DD/YY format |

| System Time        | Changes system time, time must be entered in HH:MM:SS format.   |

|                    |                                                                 |

| Access Level       | Displays current access level, default is<br>Administrator      |

#### Table 4-2: BIOS Main Setup Menu

# 4.3 Advanced Setup

Select the Advanced tab from the setup screen to enter the Advanced BIOS Setup screen. You can select any of the items in the left frame of the screen, such as SuperIO Configuration, to go to the submenu for that item. Display an Advanced BIOS Setup option by highlighting it using the < Arrow > keys. The Advanced BIOS Setup options are as follows.

| Item                               | Detail                                                                                             |  |

|------------------------------------|----------------------------------------------------------------------------------------------------|--|

| Legacy OpROM Support               |                                                                                                    |  |

| Launch PXE<br>OpROM                | Enables or disables legacy network device (default is Disabled)                                    |  |

| Launch Storage<br>OpROM            | Enables/disables the option for Legacy Mass Storage Devices with option ROM (default is Enabled)   |  |

| Clock Spread<br>Spectrum           | Enables/disables spread spectrum for clock                                                         |  |

| WatchDog Timer                     | Shows whether the WatchDog Timer is enabled (default is Disabled)                                  |  |

| PCI Subsystem<br>Settings          | Allows viewing and configuration of PCI and PCIe<br>Subsystem settings                             |  |

| ACPI Settings                      | Enables/disables AXCPI auto configuration (default is Disabled)                                    |  |

| CPU Configuration                  | Displays processor type, speed, system bus speed, etc.                                             |  |

| PCI Express Ports<br>Configuration | Enables/disables PCI Express ports and configures bus<br>and resource padding                      |  |

| SATA Configuration                 | Sets SATA mode and enables/disables SATA controller                                                |  |

| Intel Video<br>Configuration       | Sets Intel Video function                                                                          |  |

| USB Configuration                  | Provides USB support and lists the devices attached to the USB port (keyboard, mouse, and one hub) |  |

| H/W Monitor                        | Displays voltages on the backplane connector<br>(+3.3 V, +5.0 V, +12 V, 5 VSB, and Vbat)           |  |

| Thermal<br>Configuration           | Sets platform thermal configuration and Intelligent Power Sharing                                  |  |

| Temperature<br>Monitor             | Shows the current operating temperature inside the controller.                                     |  |

#### Table 4-3: BIOS Advanced Setup Menu

# 4.4 Chipset Configuration

| Item                          | Detail                                                                                                               |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------|

| North Bridge<br>Configuration | Provides memory and PCIe compliance information                                                                      |

| South Bridge<br>Configuration | Provides SMBus, GbE Controller, Wake on LAN,<br>Audio, USB Configuration, and PCIe Port<br>Configuration information |

### Table 4-4: BIOS Chipset Configuration Menu

# 4.5 Boot Setup

| Item                             | Detail                                                                 |  |

|----------------------------------|------------------------------------------------------------------------|--|

| Boot Configuration               |                                                                        |  |

| Quiet Boot                       | When disabled, allows POST messages to be viewed (default is Enabled). |  |

| Bootup NumLock<br>State          | Selects default keyboard number lock setting                           |  |

|                                  |                                                                        |  |

| CSM16 Module<br>Version          | Displays the version of the CSM16 module, e.g. 07.60                   |  |

|                                  |                                                                        |  |

| Gate A20 Active                  | Allows GA20 to be disabled by BIOS                                     |  |

| Option ROM<br>Messages           | Sets display mode for Option ROM                                       |  |

| Interrupt 19 Capture             | Allows Option ROMs to trap Int 19                                      |  |

| Boot Option Prioritie            | riorities                                                              |  |

| Boot Option #1                   | Allows selection of the primary boot source (default is the SATA HDD)  |  |

| Boot Option #2                   | Allows selection of the secondary boot source (default is Disabled)    |  |

|                                  |                                                                        |  |

| Network Device BBS<br>Priorities | Sets the order of legacy devices in this group                         |  |

| Hard Drive BBS<br>Priorities     | Sets the order of legacy devices in this group                         |  |

### Table 4-5: BIOS Boot Setup Menu

# 4.6 Security Setup

The system can be configured to require all users to enter a password (either Administrator or User) every time the system boots or when Setup is executed. Administrators and User passwords activate different levels of security.

If passwords are used, the system prompts for a three- to twentycharacter password. Typed passwords are not displayed.

| Item                       | Details                                             |

|----------------------------|-----------------------------------------------------|

| Password Descr             | iption                                              |

| Administrator<br>Password  | Sets an administrative level password for the BIOS. |

| User Password              | Sets user level passwords for the BIOS.             |

| HDD Security Configuration |                                                     |

| HDDO: INTEL<br>SSDSA2      | sets HDD password                                   |

#### Table 4-6: BIOS Security Setup Menu

Passwords are not recoverable. Please ensure that all passwords are recorded elsewhere. If your passwords are lost, NVRAM must be erased and reconfigured.

# 4.7 Save & Exit Setup

The following options for saving and exiting can be chosen in this menu.

# Save Changes and Exit

- Discard Changes and Exit

- Save Changes and Exit

- Discard Changes and Reset

- Save Changes and Reset

# Save Option

- Save Changes

- Discard Changes

- Restore Defaults

- ► Save as User Defaults

- Restore User Defaults

The "Restore the default values for all setup options" selection does not restore the original boot priority sequence. You must use the Boot Setup Menu (see Section 4.5: Boot Setup) to manually restore the boot priority sequence.

This page intentionally left blank.

# Appendix A - PXI Trigger I/O Function Reference

This appendix describes use of the PXI trigger I/O function library for the PXIe-3975 controller, to program routing of trigger signals between the trigger I/O SMB connector on the faceplate and the PXI trigger bus on the backplane.

# A.1 Data Types

The PXIe-3975 library uses these data types in pxitrigio.h in the directory X:\ADLINK\PXI Trigger IO\Include. It is recommended that you use these data types in your application programs. The table shows the data type names, ranges, and corresponding data types in C/C++, Visual Basic, and Delphi for reference.

|      |                            |                                 |                                   | Туре                                                                             |                    |

|------|----------------------------|---------------------------------|-----------------------------------|----------------------------------------------------------------------------------|--------------------|

| Туре | Description                | Range                           | C/C++<br>(for 32-bit<br>compiler) | Visual Basic                                                                     | Pascal<br>(Delphi) |

| U8   | 8-bit ASCII<br>character   | 0 to 255                        | unsigned<br>char                  | Byte                                                                             | Byte               |

| 116  | 16-bit signed integer      | -32768 to<br>32767              | short                             | Integer                                                                          | SmallInt           |

| U16  | 16-bit unsigned<br>integer | 0 to 65535                      | unsigned<br>short                 | Not supported<br>by BASIC,<br>use the<br>signed integer<br>(I16) instead         | Word               |

| 132  | 32-bit signed<br>integer   | -2147483648<br>to<br>2147483647 | long                              | Long                                                                             | LongInt            |

| U32  | 32-bit unsigned<br>integer | 0 to<br>4294967295              | unsigned<br>long                  | Not supported<br>by BASIC,<br>use the<br>signed long<br>integer (I32)<br>instead | Cardinal           |

|      |                                               |                                                           |                                   | Туре         |                    |

|------|-----------------------------------------------|-----------------------------------------------------------|-----------------------------------|--------------|--------------------|

| Туре | Description                                   | Range                                                     | C/C++<br>(for 32-bit<br>compiler) | Visual Basic | Pascal<br>(Delphi) |

| F32  | 32-bit single-<br>precision<br>floating-point | -3.402823E38<br>to<br>3.402823E38                         | float                             | Single       | Single             |

| F64  | 64-bit double-<br>precision<br>floating-point | 1.7976831348<br>62315E308 to<br>1.7976831348<br>62315E309 | double                            | Double       | Double             |

# A.2 Function Library

This section provides detailed definitions of the functions available in the PXIe-3975 function library. Each function includes a description, list of supported cards, syntax, parameter list and Return Code information.

# A.2.1 TRIG\_Init

## Description

Initializes trigger I/O function of PXIe-3975 controller. TRIG\_Init must be called before the invocation of any other trigger I/O function.

# **Supported Controllers**

PXIe-3975, PXI-3950, PXI-3920, PXI-3910, PXI-3800

# Syntax

C/C++

I16 TRIG\_Init()

## Visual Basic

TRIG\_Init As Integer

## Parameter

None

# **Return Code**

```

ERR_NoError

ERR_BoardBusy

ERR_OpenDriverFail

ERR GetGPIOAddress

```

# A.2.2 TRIG\_Close

# Description

Closes trigger I/O function of PXIe-3975 controller, releasing resources allocated for the trigger I/O function. Users must invoke TRIG\_Close before exiting the application.

# **Supported Controllers**

PXIe-3975, PXI-3950, PXI-3920, PXI-3910, PXI-3800

# Syntax

C/C++

I16 TRIG\_Close()

Visual Basic

TRIG\_Close() As Integer

# Parameter

None

## **Return Code**

```

ERR_NoError

ERR BoardNoInit

```

# A.2.3 TRIG\_SetSoftTrg

## Description

Generates a TTL trigger signal to the trigger I/O SMB connector on the faceplate or the PXI trigger bus on the backplane by software command

# **Supported Controllers**

PXIe-3975, PXI-3950, PXI-3920, PXI-3910, PXI-3800

# Syntax

C/C++

I16 TRIG\_SetSoftTrg(U8 Status)

#### Visual Basic

```

TRIG_SetSoftTrg (ByVal status As Byte) As Integer

```

### Parameters

#### Status

Logic level of trigger signal.

Available value description:

0: Logic low

1: Logic high

## **Return Code**

ERR\_NoError ERR BoardNoInit

# A.2.4 TRIG\_Trigger\_Route

## Description

Routes the trigger signal between the trigger I/O SMB connector on the faceplate and the PXI trigger bus on the backplane. This function also allows routing of the softwaregenerated trigger signal to SMB connector or trigger bus.

## Supported Controllers

PXIe-3975, PXI-3950, PXI-3920, PXI-3910, PXI-3800

## Syntax

C/C++

```

I16 TRIG_Trigger_Route (U32 source, U32 dest,

U32 halfway)

```

#### Visual Basic

TRIG\_Trigger\_Route (ByVal source As Long, ByVal dest As Long, ByVal halfway As Long) As Integer

#### Parameters

#### source

Source of trigger routing. It can be one of the following values.

| Available value    | Description                       |

|--------------------|-----------------------------------|

| PXI_TRIG_VAL_SMB   | SMB connector on the faceplate    |

| PXI_TRIG_VAL_SOFT  | Software-generated trigger signal |

| PXI_TRIG_VAL_TRIG0 | PXI trigger bus #0                |

| PXI_TRIG_VAL_TRIG1 | PXI trigger bus #1                |

| PXI_TRIG_VAL_TRIG2 | PXI trigger bus #2                |

| PXI_TRIG_VAL_TRIG3 | PXI trigger bus #3                |

| PXI_TRIG_VAL_TRIG4 | PXI trigger bus #4                |

| PXI_TRIG_VAL_TRIG5 | PXI trigger bus #5                |

| PXI_TRIG_VAL_TRIG6 | PXI trigger bus #6                |

| PXI_TRIG_VAL_TRIG7 | PXI trigger bus #7                |

dest

Destination of trigger routing. It can be one of the following values.

| Available value    | Description                    |

|--------------------|--------------------------------|

| PXI_TRIG_VAL_SMB   | SMB connector on the faceplate |

| PXI_TRIG_VAL_TRIG0 | PXI trigger bus #0             |

| PXI_TRIG_VAL_TRIG1 | PXI trigger bus #1             |

| PXI_TRIG_VAL_TRIG2 | PXI trigger bus #2             |

| PXI_TRIG_VAL_TRIG3 | PXI trigger bus #3             |

| PXI_TRIG_VAL_TRIG4 | PXI trigger bus #4             |

| Available value    | Description        |

|--------------------|--------------------|

| PXI_TRIG_VAL_TRIG5 | PXI trigger bus #5 |

| PXI_TRIG_VAL_TRIG6 | PXI trigger bus #6 |

| PXI_TRIG_VAL_TRIG7 | PXI trigger bus #7 |

#### halfway

Halfway point of trigger routing. This parameter is used only to route the software-generated trigger signal to the SMB connector on the faceplate. In this case, the halfway should be set as one of the trigger bus lines, otherwise as PXI\_TRIG\_VAL\_NONE.

| Available value    | Description        |

|--------------------|--------------------|

| PXI_TRIG_VAL_NONE  | No halfway point   |

| PXI_TRIG_VAL_TRIG0 | PXI trigger bus #0 |

| PXI_TRIG_VAL_TRIG1 | PXI trigger bus #1 |

| PXI_TRIG_VAL_TRIG2 | PXI trigger bus #2 |

| PXI_TRIG_VAL_TRIG3 | PXI trigger bus #3 |

| PXI_TRIG_VAL_TRIG4 | PXI trigger bus #4 |

| PXI_TRIG_VAL_TRIG5 | PXI trigger bus #5 |

| PXI_TRIG_VAL_TRIG6 | PXI trigger bus #6 |

| PXI_TRIG_VAL_TRIG7 | PXI trigger bus #7 |

#### **Return Code**

```

ERR_NOError

ERR_BoardNoInit

ERR Set Path

```

# A.2.5 TRIG\_Trigger\_Clear

## Description

Clears the trigger routing setting

## **Supported Controllers**

PXIe-3975, PXI-3950, PXI-3920, PXI-3910, PXI-3800

# Syntax

C/C++

I16 TRIG\_Trigger\_Clear()

## Visual Basic

TRIG\_Trigger\_Clear() As Integer

# Parameters

None

# **Return Code**

ERR\_NOError ERR\_BoardNoInit ERR\_Trigger\_Clr

# A.2.6 TRIG\_GetSoftTrg

# Description

Acquires the current software trigger state, with default state after system boot of Logic Low

# **Supported Controllers**

PXIe-3975, PXI-3950, PXI-3920, PXI-3910, PXI-3800

# Syntax

C/C++

I16 TRIG\_GetSoftTrg(U8 \*Status)

## Visual Basic

TRIG\_GetSoftTrg (status As Byte) As Integer

# Parameters

Status

Returns the logic level of software trigger signal

Returned value:

- 0: Logic low

- 1: Logic high

# **Return Code**

ERR\_NoError ERR\_BoardNoInit ERR\_Query\_Status

# A.2.7 TRIG\_Trigger\_Route\_Query

## Description

Acquires the current trigger signal routing path

# **Supported Controllers**

PXIe-3975, PXI-3950, PXI-3920, PXI-3910, PXI-3800

# Syntax

C/C++

```

I16 TRIG_Trigger_Route_Query (U32* source,

U32* dest, U32* halfway)

```

## Visual Basic

```

TRIG_Trigger_Route_Query (source As Long, dest

As Long, halfway As Long) As Integer

```

## Parameters

source

Returns to the current source of trigger routing, with possible values including:

| Available Definition | Defined Value |

|----------------------|---------------|

| PXI_TRIG_VAL_NONE    | 0             |

| PXI_TRIG_VAL_SMB     | 2             |

| PXI_TRIG_VAL_SOFT    | 3             |

| PXI_TRIG_VAL_TRIG0   | 111           |

| PXI_TRIG_VAL_TRIG1   | 112           |

| PXI_TRIG_VAL_TRIG2   | 113           |

| PXI_TRIG_VAL_TRIG3   | 114           |

| PXI_TRIG_VAL_TRIG4   | 115           |

| Available Definition | Defined Value |

|----------------------|---------------|

| PXI_TRIG_VAL_TRIG5   | 116           |

| PXI_TRIG_VAL_TRIG6   | 117           |

| PXI_TRIG_VAL_TRIG7   | 118           |

dest

Returns to the current destination of trigger routing, with possible values including:

| Available Definition | Defined Value |

|----------------------|---------------|

| PXI_TRIG_VAL_NONE    | 0             |

| PXI_TRIG_VAL_SMB     | 2             |

| PXI_TRIG_VAL_TRIG0   | 111           |

| PXI_TRIG_VAL_TRIG1   | 112           |

| PXI_TRIG_VAL_TRIG2   | 113           |

| PXI_TRIG_VAL_TRIG3   | 114           |

| PXI_TRIG_VAL_TRIG4   | 115           |

| PXI_TRIG_VAL_TRIG5   | 116           |

| PXI_TRIG_VAL_TRIG6   | 117           |

| PXI_TRIG_VAL_TRIG7   | 118           |

## halfway

Returns to the current halfway point of trigger routing, with possible values including:

| Available Value    | Description |

|--------------------|-------------|

| PXI_TRIG_VAL_NONE  | 0           |

| PXI_TRIG_VAL_TRIG0 | 111         |

| PXI_TRIG_VAL_TRIG1 | 112         |

| PXI_TRIG_VAL_TRIG2 | 113         |

| PXI_TRIG_VAL_TRIG3 | 114         |

| PXI_TRIG_VAL_TRIG4 | 115         |

| PXI_TRIG_VAL_TRIG5 | 116         |

| PXI_TRIG_VAL_TRIG6 | 117         |

| PXI_TRIG_VAL_TRIG7 | 118         |

# **Return Code**

ERR\_NoError ERR\_BoardNoInit ERR\_Query\_Status

# A.2.8 TRIG\_GetDriverRevision

# Description

Acquires the PXI Trigger software driver version; format of the version number is major.minor1.minor2

# **Supported Controllers**

PXIe-3975, PXI-3950, PXI-3920, PXI-3910, PXI-3800

# Syntax

C/C++

```

I16 TRIG_GetDriverRevision(unsigned short

*major, unsigned short *minor1, unsigned short

*minor2)

```

## Visual Basic

```

TRIG_GetDriverRevision (major As Integer, minor1 As Integer, minor2 As Integer) As Integer

```

# Parameters

major

Returns the major version number of the pxi trigger software driver

minor1

Returns the first minor version number of the pxi trigger software driver

minor2

Returns the second minor version number of the pxi trigger software driver

# **Return Code**

```

ERR_NoError

ERR_Query_Revision

```

# A.2.9 CONTROLLER\_GetHwRevision

### Description

Acquires the Controller Hardware version and revision number and the version of the trigger module CPLD

## **Supported Controllers**

PXIe-3975

### Syntax

C/C++

```

I16 CONTROLLER_GetHwRevision( U8* cpldMajor,

U8* cpldMinor, char* hwRevBuf,U32 hwRevBuf-

Size)

```

#### Visual Basic

```

CONTROLLER_GetHwRevision (cpldMajor As Byte,

cpldMinor As Byte, hwRevBuf As String,

hwRevBufSize As Long) As Integer

```

## Parameters

#### cpldMajor

Returns the major version number of the pxi trigger module CPLD

#### cpldMinor

Returns the first minor version number of the pxi trigger module CPLD

## hwRevBuf

Character buffer of size declared by the caller of size hwRevBufSize, returns a null-terminated string representation of the hardware revision

#### hwRevBufSize

Size of the hwRevBuf, in bytes

#### **Return Code**

```

ERR_NoError

ERR InvalidParameterValue

```

# A.2.10 CONTROLLER\_GetManufacturer

#### Description

Ascertains the hardware manufacturer

### **Supported Controllers**

PXIe-3975

## Syntax

C/C++

```

I16 CONTROLLER_GetManufacturer( char* Buf, U32

Bufsize )

```

#### Visual Basic

```

CONTROLLER_GetManufacturer (Buf As String,

Bufsize As Long) As Integer

```

### Parameters

Buf

Character buffer of size declared by the caller of size Buf-Size, returns a null-terminated string representation of the hardware manufacturer

BufSize

Size of the Buf, in bytes

```

ERR_NoError

ERR InvalidParameterValue

```

# A.2.11 CONTROLLER\_GetModel

# Description

Acquires the hardware model name

# **Supported Controllers**

PXIe-3975

# Syntax

C/C++

```

I16 CONTROLLER_GetModel( char* Buf, U32 Buf-

size )

```

# Visual Basic

```

CONTROLLER_GetModel (Buf As String, Bufsize As Long) As Integer

```

# Parameters

Buf

Character buffer of size declared by the caller of size Buf-Size, returns a null-terminated string representation of the hardware model name

BufSize

Size of the Buf, in bytes

# **Return Code**

```

ERR_NoError

ERR_InvalidParameterValue

```

# A.2.12 CONTROLLER\_GetSerialNumber

# Description

Acquires the serial number of the hardware

# **Supported Controllers**

PXIe-3975

# Syntax

# C/C++

```

I16 CONTROLLER_GetSerialNumber( char* Buf, U32

Bufsize )

```

# Visual Basic

```

CONTROLLER_GetSerialNumber (Buf As String,

Bufsize As Long) As Integer

```

# Parameters

# Buf

Character buffer of size declared by the caller of size Buf-Size, returns a null-terminated string representation of the serial number of the hardware

BufSize

Size of the Buf, in bytes

```

ERR_NoError

ERR_InvalidParameterValue

```

# Appendix B - Watchdog Timer

This appendix describes use of the watchdog timer (WDT) function library for the PXIe-3975 controller. The watchdog timer is a hardware mechanism resetting the system when the operating system or application halts. After starting, periodic reset of the watchdog timer in the application before expiry is required. Once the watchdog timer expires, a hardware-generated signal is sent to reset the system.

# **B.1 WDT Function Library**

# B.1.1 InitWDT

# Description

Initializes watchdog timer function. InitWDT must be called before the invocation of any other WDT function.

# **Supported Controllers**

PXIe-3975, PXI-3950, PXI-3920, PXI-3910

# Syntax

C/C++

```

BOOL InitWDT()

```

# Visual Basic

InitWDT() As Boolean

# Parameter

None

| True  | If watchdog timer is successfully initialized |

|-------|-----------------------------------------------|

| False | If watchdog timer fails to initialize         |

# B.1.2 SetWDT

## Description

Sets the timeout value for watchdog timer. The timeout value uses seconds as a unit. ResetWDT or StopWDT should be called prior to expiration of the watchdog timer, or the system will be reset.

# **Supported Controllers**

PXIe-3975, PXI-3950, PXI-3920, PXI-3910

# Syntax

C/C++

BOOL SetWDT (unsigned long second)

#### Visual Basic

InitWDT(ByVal second as Long) As Boolean

## Parameter

second

Specifies the timeout value of the watchdog timer.

Value Description

| Value    | Description                                                                                                                                                                                          |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 to 255 | If the value of the <i>second</i> parameter is between 0<br>and 255, the resolution of the watchdog timer is 1<br>second                                                                             |

| Over 255 | If the value of the <i>second</i> parameter exceeds 255, the resolution of the watchdog timer is 1 minute, that is, if a value of 400 is given, the actual timeout value is $400/60 + 1 = 7$ minutes |

| Τı |      | If timeout value of watchdog timer is<br>successfully set |

|----|------|-----------------------------------------------------------|

| Fá | alse | If timeout value of watchdog timer fails to be set        |

# B.1.3 StartWDT

## Description

Starts watchdog timer function. Once invoked, the watchdog timer countdown starts, and ResetWDT or StopWDT should be called before the expiration of the watchdog timer, or the system will be reset.

## **Supported Controllers**

PXIe-3975, PXI-3950, PXI-3920, PXI-3910

#### Syntax

C/C++

BOOL StartWDT()

Visual Basic

StartWDT() As Boolean

### Parameter

None

## **Return Code**

| True  | If watchdog timer starts successfully |

|-------|---------------------------------------|

| False | If watchdog timer fails to start      |

# B.1.4 ResetWDT

## Description

Resets the watchdog timer to the initial timeout value specified in SetWDT function, and ResetWDT or StopWDT should be called before the expiration of the watchdog timer, or the system will be reset.

## **Supported Controllers**

PXIe-3975, PXI-3950, PXI-3920, PXI-3910

# Syntax

C/C++

BOOL ResetWDT()

## Visual Basic

ResetWDT() As Boolean

# Parameter

None

# **Return Code**

| True  | If watchdog timer resets successfully |

|-------|---------------------------------------|

| False | If watchdog timer fails to reset      |

# B.1.5 StopWDT

## Description

Stops the watchdog timer.

# **Supported Controllers**

PXIe-3975, PXI-3950, PXI-3920, PXI-3910

# Syntax

C/C++

BOOL StopWDT()

## Visual Basic

StopWDT() As Boolean

# Parameter

None

| True  | If watchdog timer stops successfully |

|-------|--------------------------------------|

| False | If watchdog timer fails to stop      |

# **Important Safety Instructions**

For user safety, please read and follow all **instructions**, **WARNINGS**, **CAUTIONS**, and **NOTES** marked in this manual and on the associated equipment before handling/operating the equipment.

- ► Read these safety instructions carefully.

- ► Keep this user's manual for future reference.

- Read the specifications section of this manual for detailed information on the operating environment of this equipment.

- When installing/mounting or uninstalling/removing equipment:

- ▷ Turn off power and unplug any power cords/cables.

- ► To avoid electrical shock and/or damage to equipment:

- ▷ Keep equipment away from water or liquid sources;

- ▷ Keep equipment away from high heat or high humidity;

- Keep equipment properly ventilated (do not block or cover ventilation openings);

- Make sure to use recommended voltage and power source settings;

- Always install and operate equipment near an easily accessible electrical socket-outlet;

- Secure the power cord (do not place any object on/over the power cord);

- Only install/attach and operate equipment on stable surfaces and/or recommended mountings; and,

- If the equipment will not be used for long periods of time, turn off and unplug the equipment from its power source.

- Never attempt to fix the equipment. Equipment should only be serviced by qualified personnel.

- A Lithium-type battery may be provided for uninterrupted, backup or emergency power.

Risk of explosion if battery is replaced with an incorrect type; please dispose of used batteries appropriately.

- Equipment must be serviced by authorized technicians when:

- ▷ The power cord or plug is damaged;

- > Liquid has penetrated the equipment;

- ▷ It has been exposed to high humidity/moisture;

- It is not functioning or does not function according to the user's manual;

- ▷ It has been dropped and/or damaged; and/or,

- ▷ It has an obvious sign of breakage.

# **Getting Service**

Contact us should you require any service or assistance.

#### ADLINK Technology, Inc.

Address: 9F, No.166 Jian Yi Road, Zhonghe District New Taipei City 235, Taiwan 新北市中和區建一路 166 號 9 樓 Tel: +886-2-8226-5877 Fax: +886-2-8226-5717 Email: service@adlinktech.com

#### Ampro ADLINK Technology, Inc.

Address: 5215 Hellyer Avenue, #110, San Jose, CA 95138, USA Tel: +1-408-360-0200 Toll Free: +1-800-966-5200 (USA only) Fax: +1-408-360-0222

Email: info@adlinktech.com

#### ADLINK Technology (China) Co., Ltd.

Address: 上海市浦东新区张江高科技园区芳春路 300 号 (201203) 300 Fang Chun Rd., Zhangjiang Hi-Tech Park, Pudong New Area, Shanghai, 201203 China

Tel: +86-21-5132-8988

Fax: +86-21-5132-3588

Email: market@adlinktech.com

#### **ADLINK Technology Beijing**

Address: 北京市海淀区上地东路 1 号盈创动力大厦 E 座 801 室(100085) Rm. 801, Power Creative E, No. 1, B/D Shang Di East Rd., Beijing, 100085 China

- Tel: +86-10-5885-8666

- Fax: +86-10-5885-8625

- Email: market@adlinktech.com

#### ADLINK Technology Shenzhen

Address: 深圳市南山区科技园南区高新南七道 数字技术园 A1 栋 2 楼 C 区 (518057) 2F, C Block, Bldg. A1, Cyber-Tech Zone, Gao Xin Ave. Sec. 7, High-Tech Industrial Park S., Shenzhen, 518054 China Tel: +86-755-2643-4858 Fax: +86-755-2664-6353

Email: market@adlinktech.com

#### ADLINK Technology, Inc. (French Liaison Office)

Address: 15 rue Emile Baudot, 91300 Massy CEDEX, France Tel: +33 (0) 1 60 12 35 66 Fax: +33 (0) 1 60 12 35 66 Email: france@adlinktech.com

#### **ADLINK Technology Japan Corporation**

| Address: | 〒101-0045 東京都千代田区神田鍛冶町 3-7-4            |

|----------|-----------------------------------------|

|          | 神田 374 ビル 4F                            |

|          | KANDA374 Bldg. 4F, 3-7-4 Kanda Kajicho, |

|          | Chiyoda-ku, Tokyo 101-0045, Japan       |

| Tel:     | +81-3-4455-3722                         |

| Fax:     | +81-3-5209-6013                         |

| Email:   | japan@adlinktech.com                    |

#### ADLINK Technology, Inc. (Korean Liaison Office)

| Address: | 서울시 서초구 서초동 1675-12 모인터빌딩 8층                    |

|----------|-------------------------------------------------|

|          | 8F Mointer B/D,1675-12, Seocho-Dong, Seocho-Gu, |

|          | Seoul 137-070, Korea                            |

| Tel:     | +82-2-2057-0565                                 |

| Fax:     | +82-2-2057-0563                                 |

| Email:   | korea@adlinktech.com                            |

#### ADLINK Technology Singapore Pte. Ltd.